TECHNICAL UNIVERSITY OF DENMARK

Ph.D. Thesis

# MICROMACHINED INTEGRATED 2D TRANSDUCERS FOR SUPER RESOLUTION ULTRASOUND IMAGING

Author: Rune Sixten Grass Supervisors: Prof. Erik V. Thomsen Prof. Jørgen A. Jensen

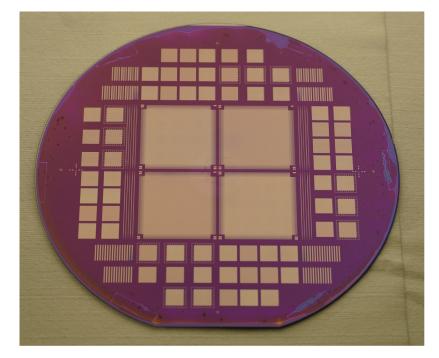

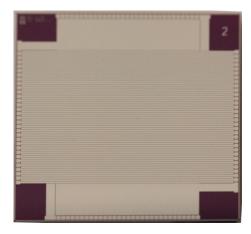

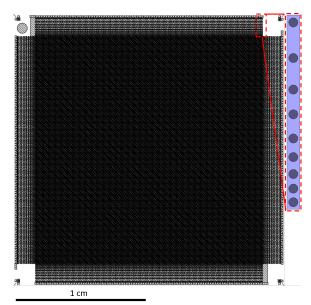

30<sup>th</sup> August 2022 Kgs. Lyngby, Denmark **Cover image:** A row-column addressed ultrasound probe developed in this work and presented in [1].

Technical University of Denmark Department of Health Technology Ørsteds Plads 345C 2800 Kgs. Lyngby DENMARK Web: www.healthtech.dtu.dk E-mail: healthtech.info@dtu.dk Author e-mail: rungra@dtu.dk

# Preface

This PhD thesis has been submitted to the Technical University of Denmark, in partial fulfilment of the requirements for the degree of Doctor of Philosophy. The research presented in this thesis has been conducted in the period from May 2019 to August 2022, including an extension period of four months, at DTU Health Technology, Technical University of Denmark. The project has been supervised by Professor Erik Vilain Thomsen and co-supervised by Professor Jørgen Arendt Jensen. During this project, the author has had the privilege attending of attending three international conferences. These are the IEEE International Ultrasonics Symposia in 2019 (United Kingdom, Scotland), 2020 (Virtually in USA, Las Vegas) and 2021 (China, Xi'an).

Rune Sixten Grass

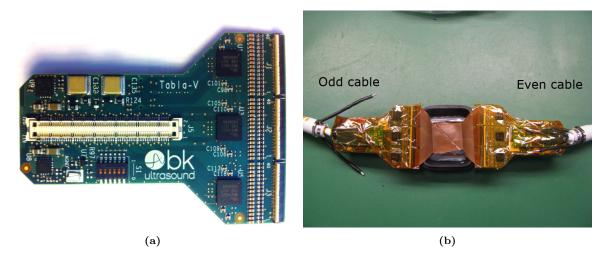

Rune Sixten Grass Technical University of Denmark Kgs. Lyngby, August 2022

### Summary

Medical ultrasound imaging is a widely used real-time technique for non-invasive diagnostics. Conventional ultrasonics 1D linear probes produce 2D images of the human body. Organs and tissues are, however, not confined to a 2D plane in the body. Vital information out of plane may therefore be lost due to the three dimensional nature of the organ and any movement of the probe. A major drive in the field of ultrasound is therefore to progress towards 3D ultrasound imaging using 2D arrays. To achieve a good focus and a high resolution, a large number of elements are needed, which translates to probes with large surface areas. In fully addressed 2D matrix arrays, this increases the complexity of the underlying technology. The number of interconnections needed in probe will also scale with,  $N^2$ , which quickly makes the process infeasible for large arrays with a high channel or element count, N.

Recently, a different type of technology using a row-addressing element scheme has been introduced. This reduced the complexity of the arrays by addressing only the N row and N column elements, and the required number of interconnects is only 2N.

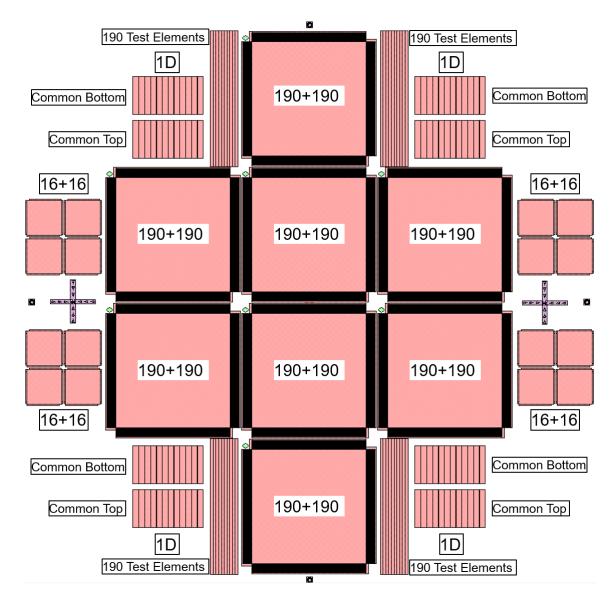

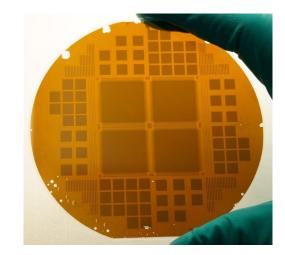

The main goal of this project has to develop large scale 2D 190+190 row-column-addressed (RCA) capacitive micromachined ultrasonic transducer (CMUT) arrays for the use in three dimensional real-time volumetric imaging. The CMUT platform was chosen as offers a high degree of flexibility, low self-heating and a large bandwidth beneficial for imaging applications. This has been achieved through the successful fabrication of two chip designs. These were based on two different fabrication techniques, and investigated to produce stable and reliable transducers. The techniques are using the local oxidation of silicon (LOCOS) based process combining fusion and anodic bonding with highly doped silicon as bottom electrodes, and using a purely anodic bonding process with metal bottom electrodes. They each have their advantages as CMUT platforms for building arrays with a uniform pressure output for all elements.

These chips were integrated in custom made hand-held transducer probes. One of these probes being a modular prototype probe for rapid prototyping developed in this research group. The electrical and acoustical performance of the two transducers were evaluated, and the 3D imaging capabilities for one of them was demonstrated. The imaging depth was found to be 3.6 cm. In conclusion, results show that the row-column technology is a realistic alternative to matrix probes for volumetric imaging. Furthermore, it is shown that the two processing techniques can be used as viable platforms for producing stable transducers. Further development is needed for achieving optimal performance.

# Resumé

Medicinsk ultralydsbilleddannelse er en hyppigt anvendt metode til at udføre ikke-invasiv diagnostik i realtid. Konventionelle 1D ultralydsprober bliver brugt til at tage 2D-billeder af den menneskelige krop. Kroppens væv og organer er dog ikke begrænset til at ligge i et 2D-plan i kroppen. Der kan derfor gå vital information tabt under en scanning fra organer som befinder ude af planet. Dette kan nemt forekomme ved bevægelser af organet eller hvis proben flyttes. En stor indsats inden for ultralydsfeltet har derfor været at gå mod 3D ultralydsbilleddannelse ved brug af 2D-arrays. For at opnå god fokusering og en høj opløsning er et stort antal elementer nødvendigt. Dette betyder at prober med et stort overfladeareal kræves. Fuldt adresseret 2D matrix-arrays kan bruges til dette formål, men dette øger kompleksiteten af den bagvedlæggende teknologi. Antallet af elektriske forbindelse krævet skalere med  $N^2$ , hvilket hurtigt gør processen nær umulig for store arrays med et højt antal kanaler eller elementer, N. For nylig er en anden type teknologi, der anvender en rækkesøjle adresserings metode for elementerne, blevet introduceret. Dette reducerer kompleksiteten af 2D arrays ved, at der kun skal adresseres N række- og N kolonneelementer. Det nødvendige antal elektriske forbindelser er derfor kun 2N.

Hovedmålet med dette projekt er at udvikle store 2D 190+190 række-kolonne-adresserede (RCA) CMUT-arrays til brug i tredimensionel volumetrisk billeddannelse i realtid. CMUT'en som Fabrikationsplatform er blevet valgt på grund af at den tilbyder en høj grad af fleksibilitet, lav selvopvarmning og en stor båndbredde som er gavnlig for billeddannelse. Dette er opnået ved at fremstille to vellykkede chipdesigns. Disse var baseret på to forskellige fremstillingsteknikker og er undersøgt med det mål at kunne producere stabile og pålidelige transducere. Den ene teknisk er baseret på den såkaldte lokale oxidation af silicium (LOCOS), som er en proces der kombinerer fusion og anodisk bonding med et højt doteret silicium substrat som bundelektroder. Den anden teknik anvender en anodisk bonding proces med bundelektroder af metal. De har hver deres fordele som CMUT-platforme til at fremstille store arrays arrays med et ensartet tryk output for alle elementerne. Disse chips blev integreret i håndholdte transducerprober. En af disse prober er en modulær prototypeprobe til hurtig prototyping, og er udviklet i denne forskningsgruppe.

Den elektriske og akustiske ydeevne af de to transducere blev evalueret, og muligheder for at udføre 3D-billeddannelse blev demonstreret for en af dem. Billeddannelse blev vist muligt ned til en dybde på 3,6 cm. Som konklusion viser resultaterne, at række-søjle-teknologien er et realistisk alternativ til matrixprober til 3D volumetrisk billeddannelse. Endvidere er det vist, at de to fremstillingsmetoder kan bruges som mulige platforme til fremstilling af stabile transducere. Videre udvikling er nødvendig for at opnå optimal ydeevne.

# Acknowledgements

First of all I would like to thank my main supervisor Professor Erik V. Thomsen and my co-supervisor Professor Jørgen Arendt Jensen. I thank you for your immense guidance and many interesting discussions both in the MEMS and CFU group. I am truly happy that I have had the opportunity to be a part of this research project in a group working on state-of-the-art ultrasonic devices.

I have learned a great many things from you Erik. Your great optimism, patience and both moral and academic support has helped me through the ups and downs of this PhD thesis, without which I am uncertain if I would have finished.

I would like to sincerely thank my colleagues at DTU Health Technology and in the MEMS group, both current and former. I thank my PhD peers, both in and out of the cleanroom, for providing a social and positive atmosphere. Thank you for always being there for both private and interesting CMUT related research discussion. A special thanks if given to Martin Lind Ommen and my fellow Master's and then PhD students Stine Løvholt Grue Pedersen and Kitty Steenberg for the great moral support.

For the great help and support during the various fabrications processes in the cleanroom facilities, I would like to extend my thanks to the staff at DTU Nanolab (former DTU Danchip). Without their help, this project would not have been possible.

I would also like to thank our Christopher Beers and our partners at BK Medical for their collaboration, including their branch in Herlev, Denmark, and in State College, PA, USA

Last, but not least, a huge thanks goes to my close friends, my mother and my late father for always supporting me.

A cknowledgements

# Acronyms

| AC<br>AFM<br>AIMS | alternating current<br>atomic force microscope<br>Acoustic Intensity Measurement System AIMS<br>III |

|-------------------|-----------------------------------------------------------------------------------------------------|

| AR                | augmented reality                                                                                   |

| ASE               | advanced silicon etcher                                                                             |

| ASIC              | application specific integrated circuit                                                             |

| BCB               | benzocyclobutene                                                                                    |

| BHF               | buffered hydrofloric acid                                                                           |

| BOX               | buried oxide                                                                                        |

| CCB               | chip carrier board                                                                                  |

| CFU               | Center for Fast Ultrasound Imaging                                                                  |

| CMP               | chemical mechanical polishing                                                                       |

| CMUT              | capacitive micromachined ultrasonic transducer                                                      |

| DC                | direct current                                                                                      |

| DOE               | design of experiments                                                                               |

| DREM              | deposit, remove, etch, multistep                                                                    |

| DRIE              | deep reactive-ion etch                                                                              |

| DSP               | double-side polished                                                                                |

| EMI               | electromagnetic interference                                                                        |

| FEM               | finite element method                                                                               |

| FFT               | fast Fourier transform                                                                              |

| FPM               | fully populated matrix                                                                              |

| FWHM              | full-width-half-maximum                                                                             |

| HCP               | hexagonal close packed                                                                              |

| HF                | hydrofloric acid                                                                                    |

| IBE               | ion-beam etcher                                                                                     |

| КОН               | potassium hydroxide                                                                                 |

| LOCOS             | local oxidation of silicon                                                                          |

| LPCVD                                    | low pressure chemical vapour deposition                                                                                                                                       |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MLA                                      | maskless aligner                                                                                                                                                              |  |

| NIL                                      | nano imprint lithography                                                                                                                                                      |  |

| PCB<br>PDMS<br>PRF<br>PSF<br>PSOI<br>PZT | printed circuit board<br>polydimethylsiloxane<br>pulse repetition frequency<br>point spread function<br>poly-silicon-on-insulator<br>lead zirconium titanate                  |  |

| RCA<br>RIE<br>RoHS<br>RTV                | row-column-addressed<br>reactive-ion etching<br>reduction of hazardous substances<br>room temperature vulcanizing                                                             |  |

| SA<br>SARUS<br>SEM<br>SNR<br>SOI<br>SSP  | synthetic aperture<br>synthetic aperture real-time ultrasound system<br>scanning electron microscopy<br>signal to noise ratio<br>silicon-on-insulator<br>single-side polished |  |

| TOBE                                     | top-orthogonal-to-bottom electrode                                                                                                                                            |  |

| UV                                       | ultraviolet                                                                                                                                                                   |  |

# Contents

| $\mathbf{P}$ | reface                                                                                                                                                                                                                                                                                                                                                                    | ii                                                                                                                                                                                |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Sı           | Summary                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                   |  |  |  |

| R            | Lesumé                                                                                                                                                                                                                                                                                                                                                                    | $\mathbf{iv}$                                                                                                                                                                     |  |  |  |

| A            | cknowledgements                                                                                                                                                                                                                                                                                                                                                           | $\mathbf{v}$                                                                                                                                                                      |  |  |  |

| $\mathbf{A}$ | cronyms                                                                                                                                                                                                                                                                                                                                                                   | viii                                                                                                                                                                              |  |  |  |

| 1            | Introduction1.1CMUT1.23D imaging1.32D CMUT arrays1.4Designing large CMUT arrays1.4.1Electrode resistance1.4.2Substrate coupling1.5The super resolution imaging project1.6This PhD project1.7Publications1.8Thesis outline                                                                                                                                                 | $     \begin{array}{r}       1 \\       2 \\       4 \\       5 \\       6 \\       6 \\       9 \\       9 \\       9 \\       10 \\       11 \\       12 \\       \end{array} $ |  |  |  |

| 2            | CMUT RC design2.1 Determining CMUT design parameters2.1.1 Frequency and size of the array2.1.2 Element pitch2.1.3 Cell layout2.1.4 Plate thickness2.1.5 Gap and pull-in voltage2.1.6 Finite element modelling2.1.7 Bragg frequency, substrate ringing and modes2.1.8 Electrode resistance2.1.9 Fabrication methods based on electrode design and style2.2 Chapter summary | $\begin{array}{c} 14 \\ 14 \\ 15 \\ 16 \\ 16 \\ 18 \\ 20 \\ 22 \\ 24 \\ 27 \\ 29 \\ 30 \end{array}$                                                                               |  |  |  |

| 3            | Wafer level characterisation         3.1       Method         3.2       Z-f         3.3       IV                                                                                                                                                                                                                                                                          | <b>31</b><br>32<br>35<br>36                                                                                                                                                       |  |  |  |

|          | $3.4 \\ 3.5$ | CV       39         Chapter summary       41                                                                                                     |

|----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| I<br>Tı  |              | OCOS-based CMUTs<br>ducer Rodent 2 (TR2) 43                                                                                                      |

| 4        | Des          | ign 45                                                                                                                                           |

|          | 4.1          | Specifications and requirements                                                                                                                  |

|          | 4.2          | Design parameters                                                                                                                                |

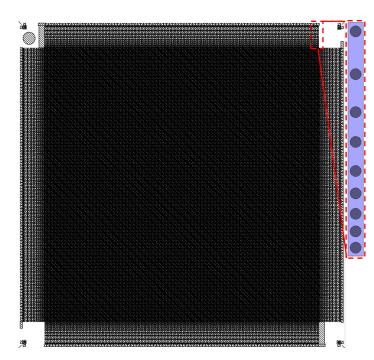

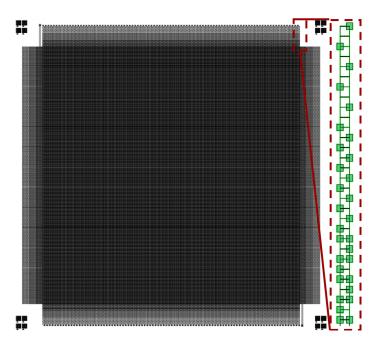

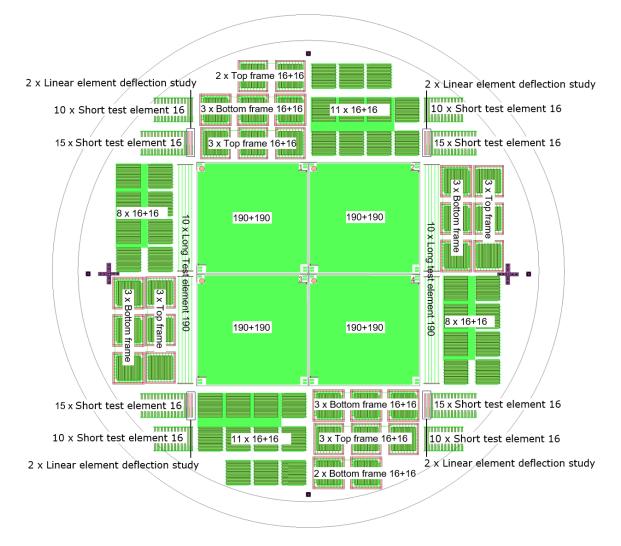

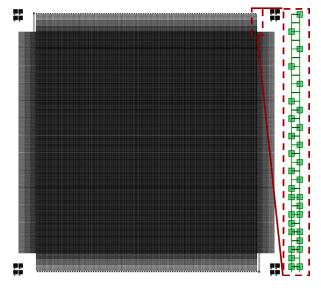

|          | 4.3          | Array Overview                                                                                                                                   |

|          | 4.4          | Chapter summary 54                                                                                                                               |

| <b>5</b> | Fab          | rication 55                                                                                                                                      |

|          | 5.1          | Methods                                                                                                                                          |

|          |              | 5.1.1 Fusion bonding $\ldots \ldots 55$               |

|          |              | 5.1.2 Anodic bonding $\ldots \ldots 56$ |

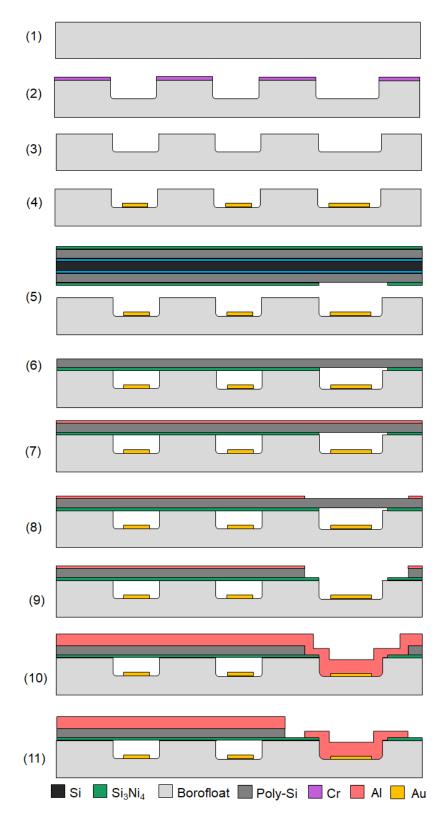

|          | 5.2          | Process                                                                                                                                          |

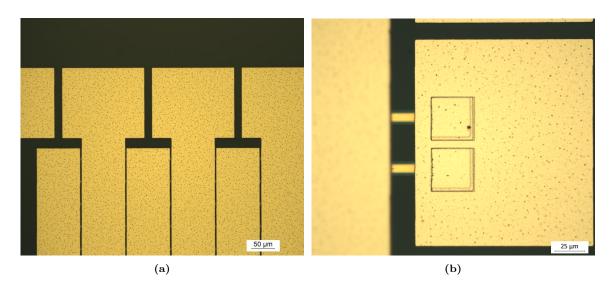

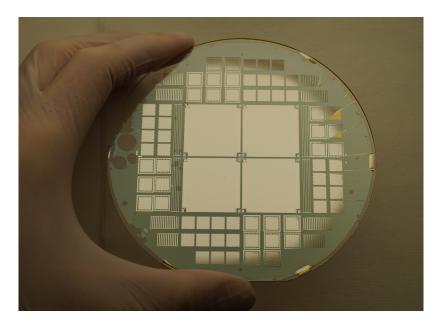

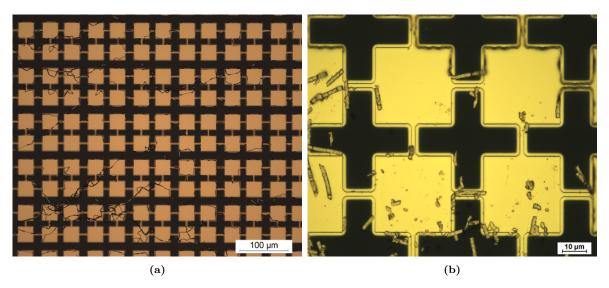

|          | 5.3          | Process result discussion                                                                                                                        |

|          | 5.4          | Chapter summary                                                                                                                                  |

| 6        | Tra          | nsducer characterisation 70                                                                                                                      |

|          | 6.1          | Electrical Characterisation                                                                                                                      |

|          |              | 6.1.1 Impedance                                                                                                                                  |

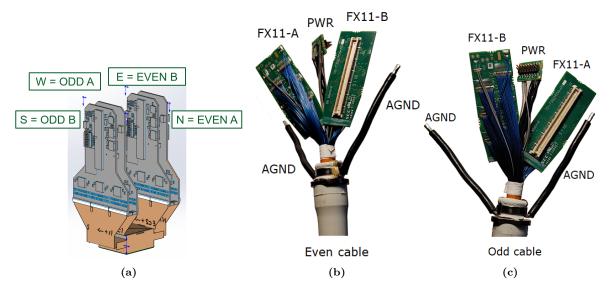

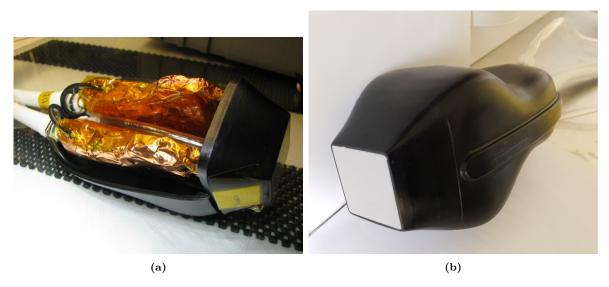

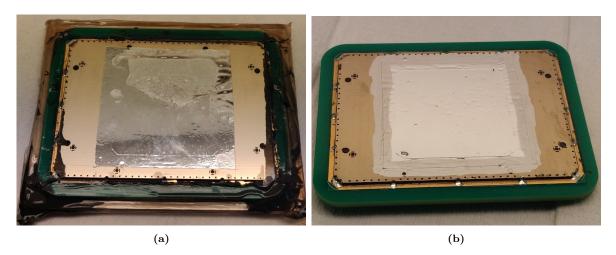

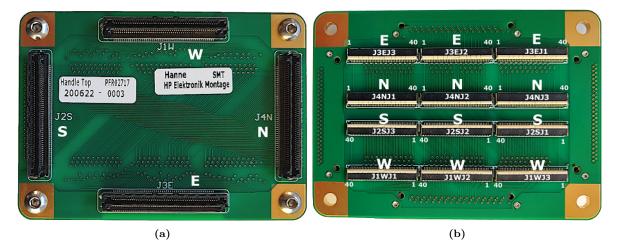

|          | 6.2          | Probe assembly                                                                                                                                   |

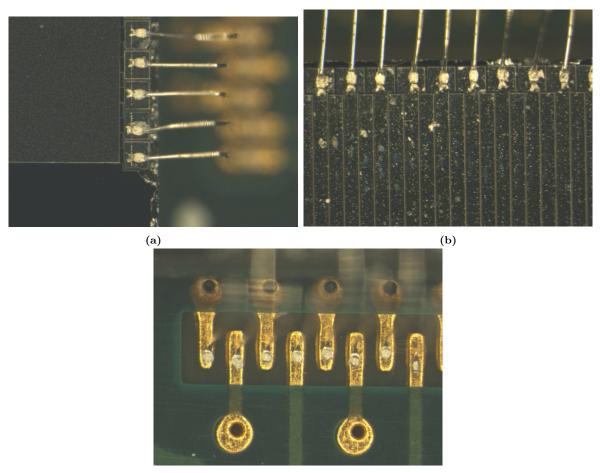

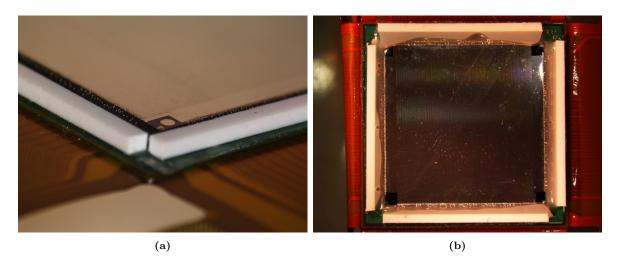

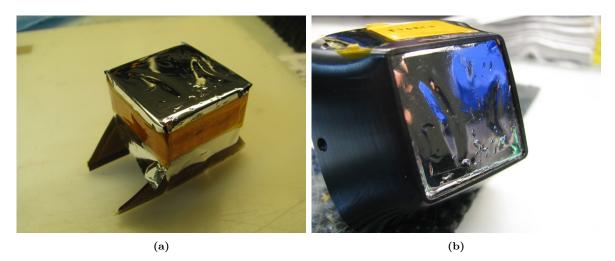

|          |              | 6.2.1 Chip mounting and wire bonding                                                                                                             |

|          |              | 6.2.2 Encapsulation and shielding                                                                                                                |

|          |              | 6.2.3 Electronics                                                                                                                                |

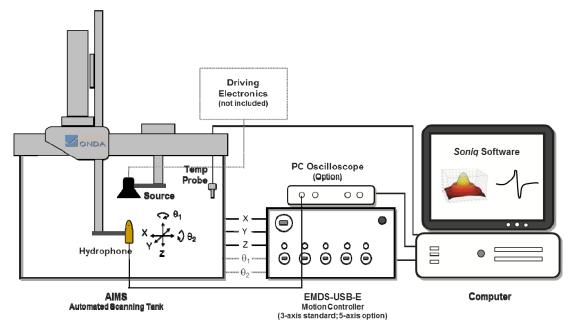

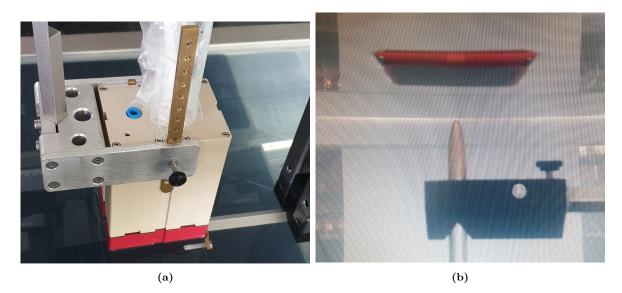

|          | 6.3          | Acoustic Characterisation                                                                                                                        |

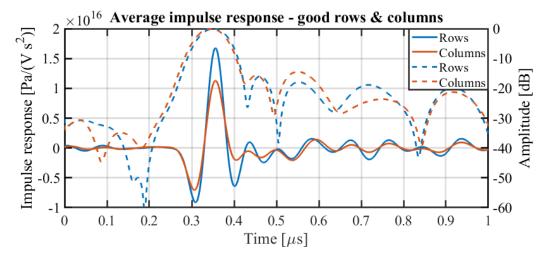

|          |              | 6.3.1 Impulse response                                                                                                                           |

|          |              | 6.3.2 Result analysis and discussion                                                                                                             |

|          |              | 6.3.3 Pressure uniformity                                                                                                                        |

|          | 6.4          | Thermal characterisation                                                                                                                         |

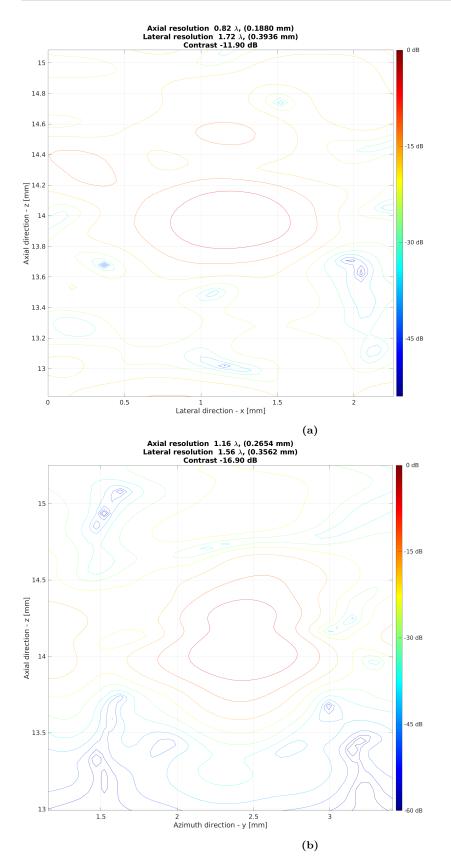

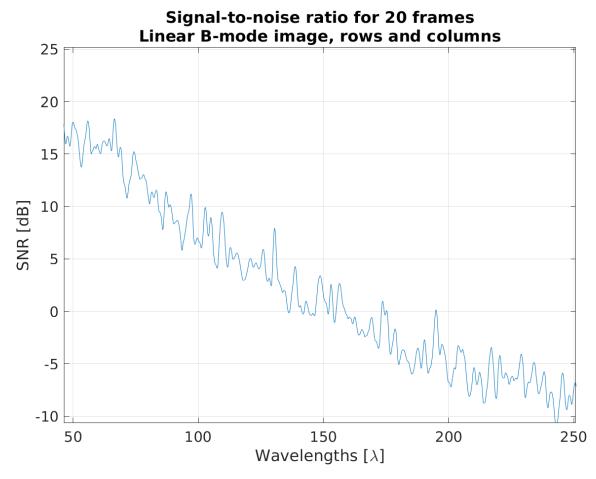

|          | 6.5          | Imaging performance                                                                                                                              |

|          |              | 6.5.1 B-mode performance of row-column array                                                                                                     |

|          | 6.6          | Chapter summary                                                                                                                                  |

|          |              |                                                                                                                                                  |

| П        |              | nodic bonding based CMUTs<br>ducor Human 1 (TH1)                                                                                                 |

| TI       | ans          | ducer Human 1 (TH1) 113                                                                                                                          |

| 7        | Des          |                                                                                                                                                  |

|          | 7.1          | Specifications and requirements                                                                                                                  |

|          | 7.2          | Design parameters - TH1 design A                                                                                                                 |

|          | 7.3<br>7.4   | Array Overview    125      Chapter summary    127                                                                                                |

|          | 7.4          | Chapter summary 127                                                                                                                              |

| 8        | Fab          | rication 128                                                                                                                                     |

|          | 8.1          | Process iterations of CMUT chips                                                                                                                 |

|          | 8.2          | Process chip A 128                                                                                                                               |

|          | 8.3          | Process Optimisation                                                                                                                             |

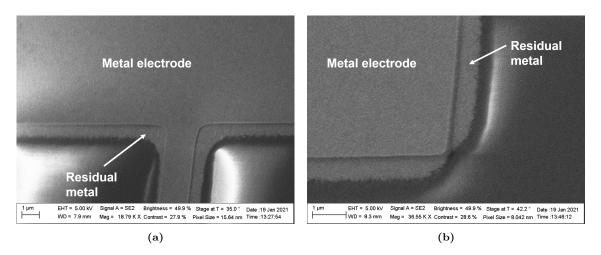

|          |              | 8.3.1 Over-etching in the IBE process 143                                                                                                        |

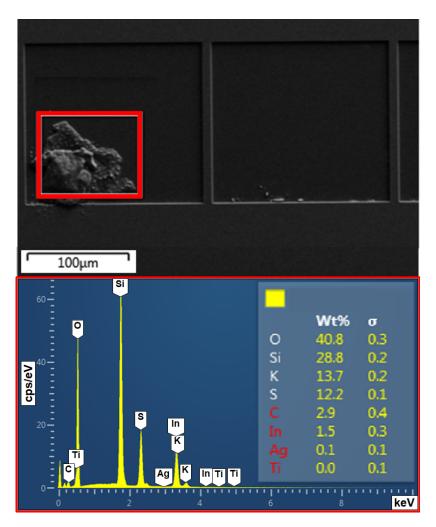

8.3.3 Gold ribbon formation in the IBE process  $\ldots \ldots 143$

143

|    |     | 8.3.4 Incomplete aluminium plugging of electrodes 14                                                     | 4  |

|----|-----|----------------------------------------------------------------------------------------------------------|----|

|    | 8.4 | Chapter summary 14                                                                                       | :5 |

| 0  | m   |                                                                                                          | ~  |

| 9  |     | nsducer Characterisation 14                                                                              |    |

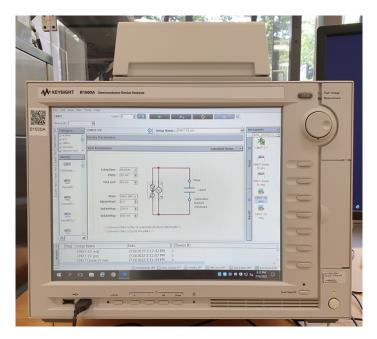

|    | 9.1 | Electrical Characterisation                                                                              | -  |

|    |     | 9.1.1 IV, Z-f and CV measurements                                                                        |    |

|    |     | 9.1.2 Impedance                                                                                          |    |

|    |     | 9.1.3 Long term stability                                                                                |    |

|    | 9.2 | Probe Assembly                                                                                           |    |

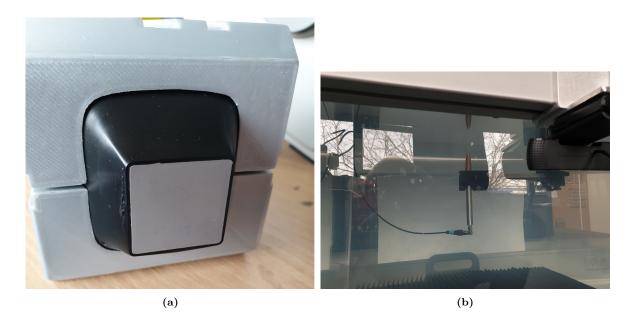

|    |     | 9.2.1 Prototype Probe                                                                                    |    |

|    |     | 9.2.2 Chip mounting and wire bonding                                                                     |    |

|    |     | 9.2.3 Encapsulation and shielding                                                                        |    |

|    |     | 9.2.4 Electronics                                                                                        | 8  |

|    | 9.3 | Acoustic Characterisation                                                                                | 1  |

|    |     | 9.3.1 Impulse response                                                                                   | '1 |

|    |     | 9.3.2 Results analysis and discussion                                                                    | 6  |

|    |     | 9.3.3 Pressure uniformity 18                                                                             | 3  |

|    | 9.4 | Chapter summary 18                                                                                       | 6  |

| 10 | Con | nclusion and outlook 18                                                                                  | 9  |

|    |     |                                                                                                          |    |

| AĮ | -   | dix A Design parameters and fabrication results 20                                                       |    |

|    |     | TH1-B design                                                                                             | 0  |

|    |     | TH1-B processing results                                                                                 | 3  |

|    | A.3 | Gold ribbons design of experiment 20                                                                     | 4  |

|    |     |                                                                                                          | -  |

| AĮ |     | dix B Process flows 20                                                                                   |    |

|    | В.1 | Main fabrication process flows                                                                           |    |

|    |     | B.1.1 Fusion anodic bonding process flow                                                                 | -  |

|    |     | B.1.2 Anodic bonding process flow                                                                        |    |

|    |     | B.1.3 PSOI process flow                                                                                  | 2  |

| A  |     | dix C Paper A - 188+188 Row-Column Addressed CMUT Transducer for                                         | ~  |

|    | Sup | ber Resolution Imaging 22                                                                                | 8  |

| AĮ |     | dix D Paper B - Wafer Level Characterization of Row-Column Addressed<br>UT Arrays 23                     | 4  |

| A  |     | dix E Paper C - Wafer bonded CMUT technology utilizing Poly-Silicon-on-<br>ulator wafers 23              |    |

| A  |     | dix F Paper D - Large Scale High Voltage 192+192 Row-Column Addressed<br>UTs Made with Anodic Bonding 24 | 5  |

| A  | -   | dix G Paper E - A Hand-Held 190+190 Row–Column Addressed CMUT<br>be for Volumetric Imaging 25            | 0  |

### Chapter 1

# Introduction

The use of medical ultrasound or ultrasonography dates back to around the middle of the 20th century [2], [3] where it was already then seen as a new tool or modality with a lot of potential for medical therapy [4]. The technology has since then grow into the multi-functional diagnostic tool we know from hospitals today in the form of lightweight hand-held transducer probes. Ultrasonic imaging is seen as a harmless and non-invasive technique when compared to other imaging techniques like standard X-ray or computed tomography (CT) scans and even magnetic resonance imaging (MRI) as no ionising rays or harmful contrast agents are used. Medical ultrasound is relatively inexpensive compared to the previously mentioned techniques and the probe is used in conjunction with a portable computer, which can placed right beside the patient. This allows doctors to obtain diagnostic images of patients in real time right at their bedside. Ultrasound however might offer poor resolution with increasing scanning depth compared to other modalities, unless the ultrasonic probe is brought closer to the tissue of interest by inserting it into the body with laparoscopic methods or the footprint of the transducer is increased.

Ultrasound images are made by mapping the echoes generated when transmitted acoustic pulses are fully or partially reflected or scattered from structures in the scanned medium. These reflections arise from an acoustic impedance mismatch in-between two types of tissue or structures in the human body. Bone in particular gives a large reflection of the signal and makes it difficult to scan structures behind bone or dense tissue. Similarly, the lungs and potentially the colon will be difficult to scan due to the presence of air, which creates large reflections.

Most ultrasonic probes used in hospitals for medical imaging are made using the poly-crystalline piezoelectric ceramic material lead zirconate titanate (PZT) which is also used for many different sensing devices, actuators, and low-power systems. These probes usually have between 64-256 long ceramic crystal elements with a width in the micrometer scale for generating ultrasound used for imaging. This device works by utilising the piezoelectric effect by applying an alternating current (AC) signal with a megahertz frequency across the crystal to make it vibrate in the same frequency. PZT has been an industry standard for several decades due to its high piezoelectric coefficient, electromechanical coupling coefficient and dielectric constant desirable for impedance matching [5]. Alternative piezoelectric ceramics such as the lead-free ceramic potassium sodium niobate (KNN) or lead magnesium niobate-lead titanate (PMNT) also exist. Ceramics different from PZT, including lead-free types, however, usually have poorer material parameters and are often more expensive, which makes PZT synonymous with piezo ceramics in ultrasound. PMNT, albeit more costly, can be grown as a single crystal and could be a likely candidate for replacing PZT due to its excellent piezoelectric properties.

The PZT arrays used in probes are often fabricated using the dice-and-fill method [6]. Here the kerf between the crystal elements is limited by the width of the dicing blade to around  $15 \,\mu\text{m}$  [7]. This can pose a problem for high frequency probe designs, where the element width becomes comparable

to the kerf for small pitch probes. This results in a small relative active area for transmitting ultrasound, which reduces the pressure of the array. The resonance frequency of PZT crystals given by speed of sound in the material over the crystal thickness. Thus, for high frequency probes the thickness becomes small, which makes them fragile and more difficult to fabricate.

Furthermore, in the recent years there has been an increasing concern over environment and health related risks over the use of lead containing materials. As much as 100 metric tonnes of lead is used in the field of medical ultrasound each year, with approximately 90 tonnes emitted to the atmosphere. The total annual production of lead zirconium titanate (PZT) material is estimated to be around 5000 tonnes [8] of which a 60 weight percentage is comprised of lead [9]. The reduction of hazardous substances (RoHS) directive from 2006, also called the "lead-free directive", list lead as a banned substance for use in electrical and electronic equipment. The exemption is of PZT ceramics for use in medical devices, and other applications using ultrasound [10] where no optimal alternative is found. An alternative to the continued used of lead based PZT for medical ultrasonic probes is sought, which also eases the fabrication process for high frequency operation, which is used for a wide range of applications,

#### 1.1 CMUT

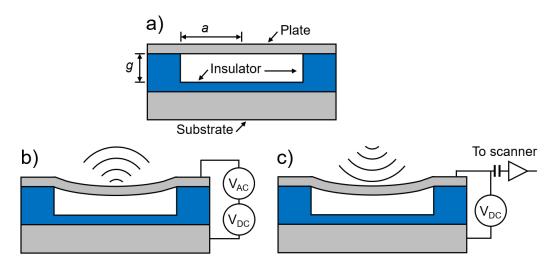

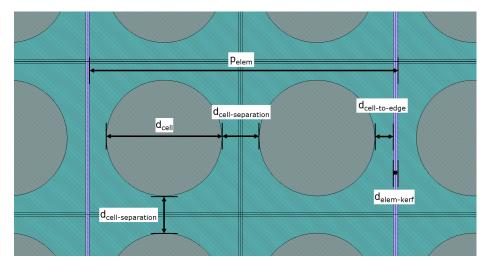

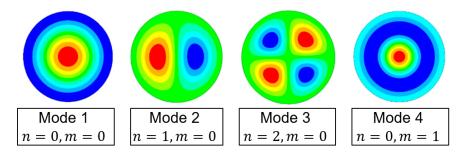

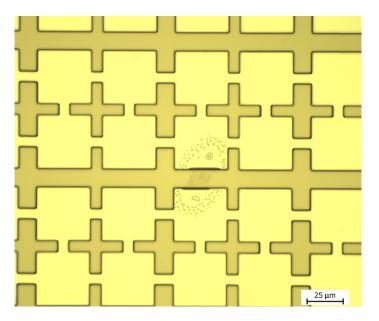

One alternative to the piezoelectric transducer is the CMUT based on silicon microfabrication. A CMUT is a small device in the micrometer range which can transmit ultrasound, much like the PZT crystal. The difference is that it instead consists of a micromachined cavity on a substrate and a vibrating plate (or membrane) separated by an electrically insulated material, such as a dielectric. Such a CMUT structure is referred to as a cell and is illustrated in Fig. 1.1. Typically it has lateral dimensions in the range of 10 µm to 100 µm, vertical dimensions in the range of 200 nm to 800 nm for the gap in the cavity, and 1 µm to 6 µm for the vibrating plate. Hundreds of these cells comprising a single element are used to transmit ultrasound in unison. These cells can be defined through the use of simple ultraviolet (UV) lithographic processes. UV lithography can make features down to  $\approx 0.6 \,\mu\text{m}$  in width and CMUT devices can therefore be made smaller than what is usually possible for piezoelectric transducers, and the pitch can more easily be controlled. This allows for an element pitch of  $\lambda/2$  to be kept for high center frequencies, which minimises grating lobes [11]. A smaller feature size and precise definition of structures also allows for easier integration with integrated circuits (ICs) on chip.

The idea of utilising a capacitive structure as an ultrasonic actuator for studying pressure fields in liquids and air was presented in the early 1990s. In an IEEE IUS conference paper from 1991 by Schindel et al. [12] describes how conventional IC manufacturing techniques can be used for constructing capacitive devices, capable of radiating ultrasound in the megahertz regime, with a fixed conductive back electrode and a suspended vibrating membrane. These studies were further developed simultaneously by Hietanen et al. in 1993 [13] (using a V-grooved backplate electrode) and in a journal paper in 1995 [14] Schindel et al. Common for these are that they use semiconductor microfabrication to create silicon bottom electrode and utilise metallised Mylar polyester foil or Kapton tape as the membrane.

The first and most influential paper accredited to the birth of what came to be known as the CMUT is a conference paper from 1994 titled "A Surface Micromachined Electrostatic Ultrasonic Air Transducer" by Matthew I. Haller and Butrus T. Khuri-Yakub [15]. This paper describes the theory of operation, fabrication and characterisation of a fully surface micromachined silicon based transducer with a 750 nm silicon nitride membrane. The air-coupled transducer operates at a resonance frequency of 1.9 MHz, and the cavity was fabricated by a sacrificial release process using a silicon dioxide layer. This study was followed by a journal paper by the same authors in 1996 [16]. Same year, broadband emission of transducer arrays with frequencies at 4 MHz, 6 MHz and 8 MHz from the same group were studied in immersion which showed a wide bandwidth in the range from 1 to 20 MHz and high signal-to-noise ratio capable of competing with piezoelectric devices [17].

Figure 1.1: Cross-sectional sketch of signel CMUT cell. a) The dimensions and components of the cell are indicated. The vibrating plate is shown with the radius of half side length a, and the substrate and insulating dielectric is shown with the vacuum gap g. b) The CMUT operating as a transmitting device, with a DC voltage bias and an AC signal is applied between the plat (top electrode) and substrate (bottom electrode) to send out an ultrasound signal. c) The CMUT operating as a receiving device, with a DC voltage bias applied and the incoming ultrasound signal converted to an AC signal for the scanner.

In 2000 the first experimental pulse-echo results on a wire phantom in immersion using a 16 element 1-D CMUT array is presented by Oralkan and Khuri-Yakub [18] and shows a B-scan image made from RF beamforming. This research was further developed in 2002 [19] [20] showing capabilities of fabricating 128 by 128 element 2-D CMUT arrays with the potential for 3-D volumetric ultrasonic imaging. Due to the large amount of interconnections needed, only a smaller sub-array was measured. A follow-up article from 2003 shows the first volumetric scans using the arrays [21].

A new type of fabrication technique for CMUT devices was presented in a paper from 2003 by Huang et al. [22] based on wafer bonding. In this technique a silicon-on-insulator (SOI) wafer is bonded to a micromachined silicon wafer with cavities through silicon direct bonding (fusion bonding) to form the transducers. The device layer of the SOI wafer is a high resistivity silicon, which when the SOI wafer is etched will form the CMUT membrane.

In 2004 and 2005, the design, fabrication and characterisation of a 64 element 3 MHz 1D CMUT probe was presented by Caliano et al. [23], [24], using sacrificial release methods and compared to a commercial PZT probe with a lens.

The same group from the Roma Tre University, presented a different type of sacrificial release method using a novel reserve fabrication process (RFP), presented by Caliano et al. in 2005 in [25]. The CMUTs are defined on top of a silicon handle substrate with a silicon nitride layer deposited. The thickness determines the CMUT plate thickness. After the CMUTs cavities have been defined through the sacrificial release method, the diced chips are wire bonded to a printed circuit board (PCB) and a backing layer is applied. The silicon handle layer can then be etching from the backside using a mixture of hydrofluoric, nitric, and acetic acids (HNA). The backside, which is now the front side, reveals the CMUT array and the nitride plate of the cells. This technique was used to fabricate a 192 element 12 MHz 1D CMUT probe, presented in 2012 by Savoia et al. [26].

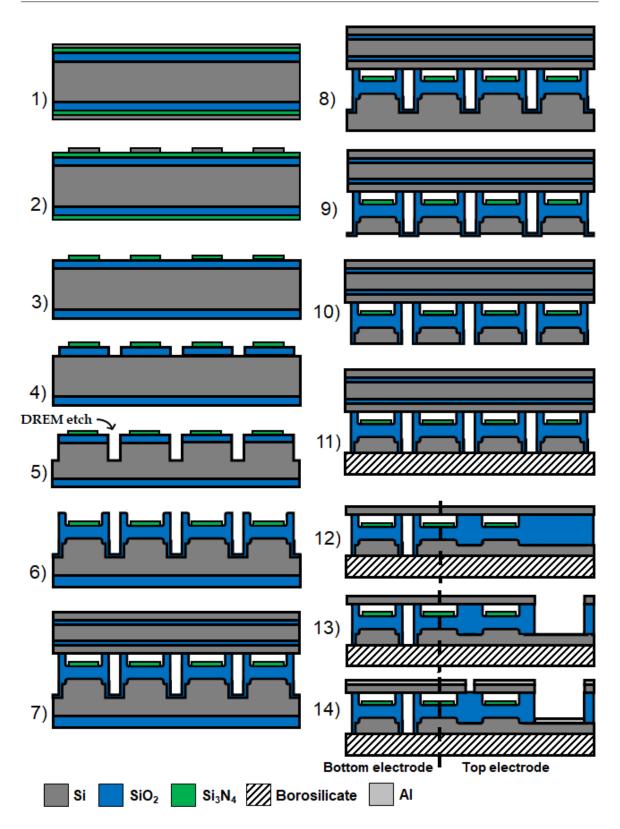

A different wafer bonding approach was demonstrated in 2009 by Olcum et al. [27] by CMUTs fabricated with anodic bonding. In this technique a glass wafer is usually structured and bonded to a silicon substrate, which is subsequently thinned to a specified plate thickness. Functional 1D linear CMUT arrays utilising anodic bonding has since been published [28]–[30].

Since the first use for 2D imaging [18], the CMUTs technology has been successfully used for fab-

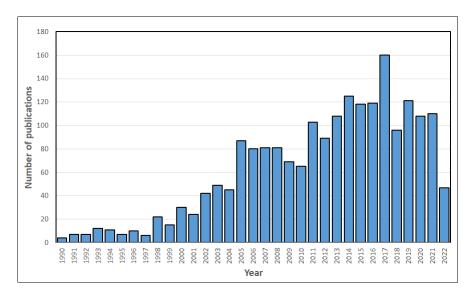

Figure 1.2: Number of CMUT publications from 1990 to 2022. This graph has been generated from the Scopus database using the following keystring: Capacitive Micromachined Ultrasonic Transducer\* OR CMUT OR CMUTS OR Electrostatic Ultrasonic Air Transducer OR Capacitive Transducer\* OR Surface Micromachined Transducer". A total of 2212 publication are listed.

rication 1D linear array probes by several academic and industrial research groups [23], [24], [26], [31]–[38] and more recently such probes have become commercially available. The field of CMUTs is rapidly expanding, which is illustrated in the Fig. 1.2 as the number of publications per year. The final count in 2022 is taken at the point in time of hand-in for this PhD thesis, which also happens right before the large International Ultrasound Symposium (IUS), where a substantial amount of CMUT papers are published.

#### 1.2 3D imaging

When ultrasound imaging is performed, it is most often the so-called B-mode or brightness mode which is used. Using a linear 1D transducer, this produces 2D gray-scale images in real time of the brightness or intensity of the reflected sound waves in the body. The images display a scanned plane orthogonal to the transducer surface with scan depth and width and at the axes. A-mode or amplitude modulation is a simpler type of ultrasound consisting of just a single intensity line, which makes up the B-mode images, and amplitude on the y-axis and imaging depth on the x-axis. M-mode, or motion mode, is a mode used for rapid imaging, where many line scans are taken in succession together with B-mode images to monitor the movement of organs and vessel boundaries. Another type of mode is the Doppler mode, which makes use of the Doppler effect to measure the directivity and velocity of the blood flow in vessels. This can be used to display full color maps of blood flow in real time by color flow mapping (CFM), which enables easier diagnosis of vascular problems. The blood direction and velocity can be colour coded as colour intensity and displayed on top of B-mode images.

Blood vessels and organs in the body will when imaged with a linear 1D transducer, however, be confined to a 2D plane. Important out of image plane information may be lost due to the three-dimensional nature of the organ and any movement of the probe. A natural further development and also a major drive in the field of ultrasound is therefore to progress towards 3D ultrasound imaging using 2D arrays.

3D volumetric imaging with ultrasonic probes can be achieved with 2D arrays. Such an array can be constructed by extending or replicating a 1D array design in the orthogonal direction N number

of times, corresponding to the element count in the 1D array. This is called a fully populated matrix (FPM) array and has  $N \times N$  elements. Each of these elements in the matrix need to be individually accessed and this requires the same amount of inter-connectors. To achieve a good focus and a high resolution with an ultrasonic probe a large number of elements are necessary.

The focusing ability is proportional to the wavelength of the ultrasonic signal and the ratio of the imaging depth to the width of the array. If the same resolution is to be kept in both dimensions of the array, the same number of elements are needed in both directions of the array. Higher resolution at a large imaging depth requires that the ultrasonic probes, and therefore also the arrays, becomes larger to maintain the ratio between depth and width.

If a 2D FPM probe should have the same resolution in both dimensions as e.g. an 1D linear probe with 190 elements, this would require  $190 \times 190 = 36100$  elements and inter-connections. This can make it highly infeasible to make large scale matrix probes.

Smaller state-of-the-art matrix probes made using PZT can be acquired from commercial suppliers from e.g. Philips (X6-1 xMATRIX array transducer with 9212 elements). Probes used for research can also be acquired through Verasonics (Matrix Array Transducer with 1024 elements  $(32 \times 32)$ ).

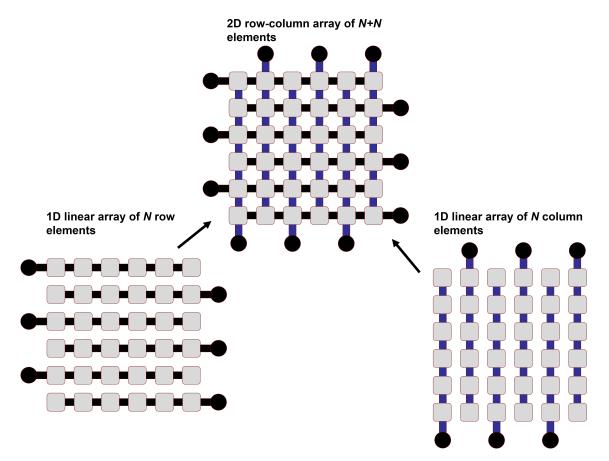

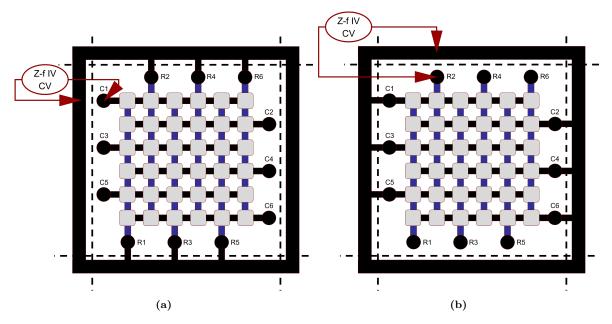

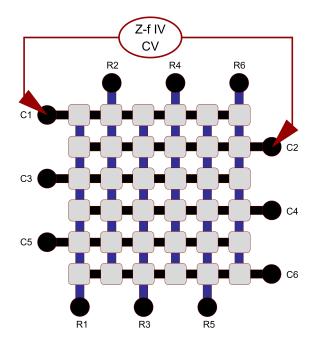

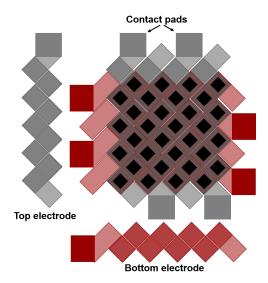

The high connection count of matrix probes can be reduced significantly by utilising other array design which use alternative element addressing schemes. Recently, a new type of scheme was proposed by Morton and Lockwood [39] as a crossed electrode design. This is a so-called RCA array. It is essentially the combination of two 1D linear array layered orthogonal to each other, illustrated in Fig. 1.3. The section where each element overlap is defined as a sub-element or a unit cell. In this scheme the long rows and columns of the array are addressed individually similar to a 1D array, instead of the corresponding single matrix elements in an FPM array. This reduced the number of connections to just N + N, which for a 190 + 190 RCA array equals 380 elements. This row-column technique has since been used by multiple research groups for fabricating arrays for 3D imaging.

It has been shown by Rasmussen and Jensen [40] that the imaging resolution of RCA arrays will always be higher for the same number of elements when compared to an FPM array, e.g. a 128+128 = 256 row-column array corresponding to a 16 matrix array. The latest details regarding the imaging capabilities of the RCA arrays for 3D volumetric super resolution imaging can be found in [41].

#### 1.3 2D CMUT arrays

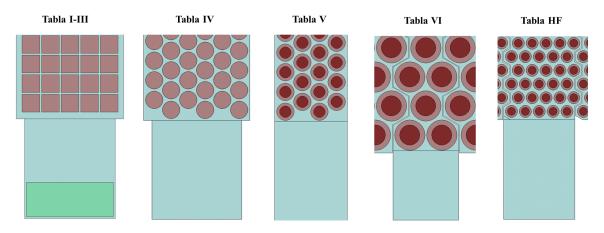

2D Row-column arrays have been fabricated with a variety of different materials and array sizes, such as using PZT, by Seo at al. as  $64 \times 64$  and  $256 \times 256$  arrays (addressed as 64 + 64 and 256 + 256 row-column arrays) [42], [43], and by Chen et al. using a combination of PZT and a P[VDF-TrFE] copolymer [44]. The row-column addressing scheme has also been presented by a Canadian ultrasonic research group from the University of Alberta with a different terminology named top-orthogonal-to-bottom electrode (TOBE). Such an array was presented using a PNM-PT electrostrictive ceramic by Latham et al. in [45]. A research probe was recently presented in our group with an integrated PZT based 62 + 62 RCA array by Engholm et al. in 2018 [46]. Commercial row-column probes made using PZT are available from Vermon and Verasonics (RC6gV Row-Column Array Transducer), which have 128+128 rows and columns with a 6 MHz center frequency. Recently prototype probe with 128+128 rows and columns with a 12 MHz center frequency was introduced by Daxsonics.

The row-column addressing scheme has also been used for CMUTs, which is the focus of this PhD thesis. These have been fabricated using many different etching and bonding methods, such as by using the sacrificial release method [47], [48], with a TOBE array architecture, adhesive wafer bonding [49], [50], fusion bonding [46], [51]–[54] and anodic bonding [55]–[57]. Some of the listed probes from this group have been integrated in hand-held probes and interfaced the scanners from the company BK Medical. These are presented in [46] as a 62+62 RCA 2D CMUT probe alongside a PZT row-column probe with also 62+62 elements, and in [54] as two 92+92 RCA 2D CMUT probes with and without integrated diverging lenses. Commercially available probes using RCA addressed

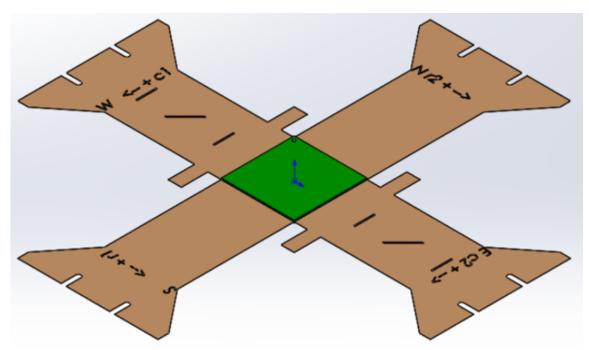

Figure 1.3: Sketch of the 2D row-column addressed array structure as a combination of two orthogonal N element 1D linear arrays with alternating electrodes pads.

CMUT technology are not yet available.

However, recently the company Butterfly Network, Inc. (Guilford, CT, USA) made a 2D CMUT transducer called Butterfly iQ. It is a type of 2D phased array matrix transducer with  $140 \times 64 = 8960$  elements, which can be used in different configurations as curved, linear and phased arrays if needed. The CMUT chips are integrate with a large application specific integrated circuit (ASIC) die. The probe is designed to be connected to a phone or tablet and be run without external power. Images are shown directly on the mobile device and can be used together guided scanning based on augmented reality (AR).

#### 1.4 Designing large CMUT arrays

It was introduced in the previous section that the 3D imaging technique utilizing RCA scheme requires a 2D row-column CMUT array with many elements to capture a 3D volume with a high resolution. It is inevitable that the trend will then be a progression towards large arrays to accommodate the elements. When designing large RCA arrays there are a number of important criteria to ensure optimal performance as well as a few choices of fabrication techniques.

#### 1.4.1 Electrode resistance

When an element is excited by an AC signal the pressure emitted along each element, whether rows or columns, and across neighbouring elements should be uniform. If this is not the case, the pressure

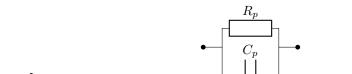

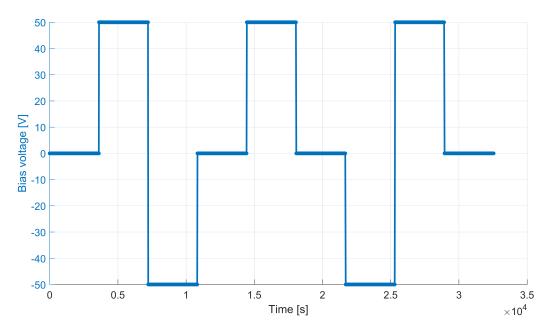

field of the array when performing imaging will not match simulated fields and can be detrimental to the image quality. The pressure drop which is a direct result of an attenuation of the voltage potential along the element can be modelled as a so-called delay-line effect [58], which can be derived from a diffusion equation describing the element potential along the element. In Section 2.1.8 this will be explained more in detail, the result, however, is a an expression describing the remaining voltage potential at the end of the element and a dimensionless product  $\omega RC$ , which can be used as a criterion when designing the arrays. The product contains the angular excitation frequency,  $\omega$ , the element electrode resistance, R, and the total capacitance of the element, C.

To keep a uniform pressure distribution, the potential drop along the element is set to a maximum of 1 %. This corresponds to an  $\omega RC$  value of

$$\omega RC \le 0.35 \tag{1.1}$$

This value, which should be as low as possible, sets requirements for the material used to fabricate the top and bottom electrodes and the techniques needed. Bottom electrodes are typically made with either deposited metal, e.g. in Al, Cr, or Au on top on an insulating substrate, or with a highly doped silicon substrate used directly as an electrode.

If silicon is used as bottom electrode material, a limit of around  $10^{21}$  cm<sup>-3</sup> which is designated as heavy doping [59], is set as the highest n-type doping level which can be achieved by doping with phosphorus [60, p. 377], which is a limit governed by the solid solubility of the dopant in silicon. A slightly higher concentration can be achieved using As instead of P.

This corresponds to a resistivity of  $10^{-4} \Omega \text{ cm} [60, \text{ p. 18}]$ . Higher concentrations can likely be achieved near the substrate surface using ion-implantation and by the pile-up effect through annealing [60], but whether these dopants are electrically active and can contribute to the conductivity is not fully known. However, it does seem possibly that even higher active donor doping levels are possible through using the chalcogen donor Te [61].

Depending on the dopant and doping level this can prove problematic for long arrays as the resistance is proportional to the length  $R \propto L$  and capacitance proportional to the electrode area  $C \propto A$ . CMUTs fabricated with a silicon substrate using fusion/direct bonding process [62], [63] requires a high temperature post annealing step at >1000 °C to fuse the dielectric insulation layer with a top plate.

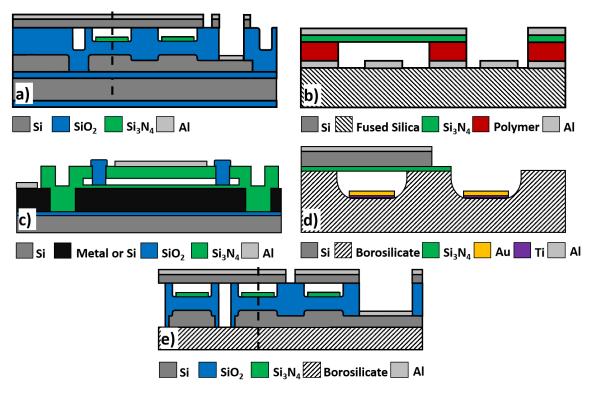

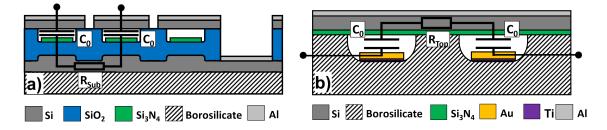

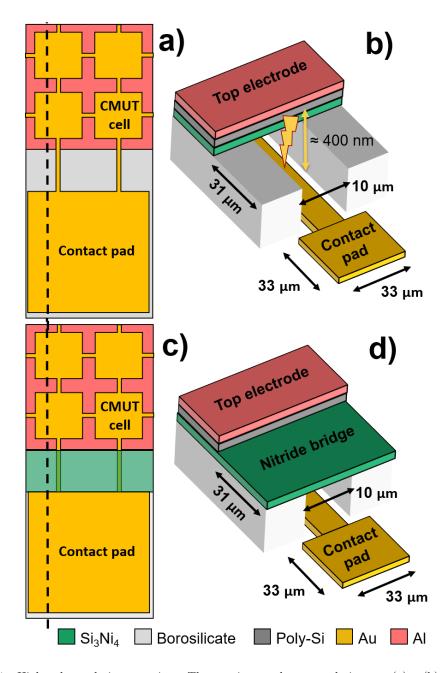

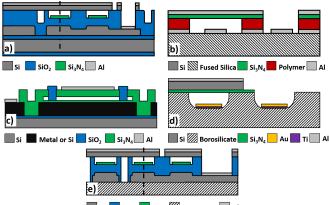

Such a device is illustrated in Fig. 1.4(a) fabricated on an SOI wafer made with direct or fusion bonding. The temperature step makes this technique incompatible with metal bottom electrodes, and one has to rely on doped silicon for the bottom electrodes to keep the resistance sufficiently low. In applications where the doped silicon wafer substrate or the silicon device layer serves as the bottom electrode, the handle or layer thickness can be increased to decrease the resistance.

Metal electrodes have a resistivity on the order of  $10^{-6} \Omega \text{ cm}$  [66], which being two orders of magnitudes lower than doped silicon, will reduce resistance problems and be sufficient for most applications, depending on the electrode shape. The use of metal electrodes and their low thermal budget limits the number of techniques which can be used for CMUTs to mainly three types.

1) Adhesive polymer bonding [67] using e.g., benzocyclobutene (BCB) [65], see Fig. 1.4(b). This is a versatile method for joining different types of substrates and top plates with a polymer spacer. The great advantage of using polymers is that they can be patterned as a standard UV-sensitive resist or using nano imprint lithography (NIL). Polymer bonding can be used with both silicon and metal bottom electrodes, here demonstrated with metal deposited and patterned on a fused silica wafer.

2) Sacrificial release methods [68], see Fig. 1.4(c). For this technique an intermediate sacrificial layer, often a metal layer, between the substrate and a dielectric layer is dissolved. This leaves CMUT cavities covered by a dielectric plate which are sealed using silicon dioxide or silicon nitride plugs. This can be used with both metal and silicon electrodes.

3) Anodic bonding [28], see Fig. 1.4(d). In this technique bottom electrodes are made by etching CMUT cavities into a glass substrate using a mask, metal electrodes are deposited and structured in

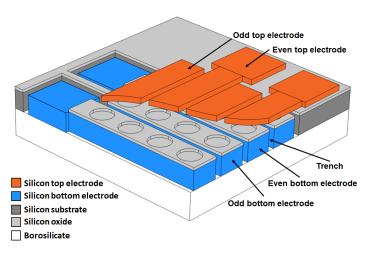

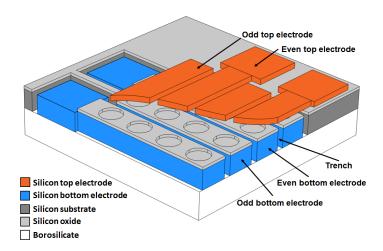

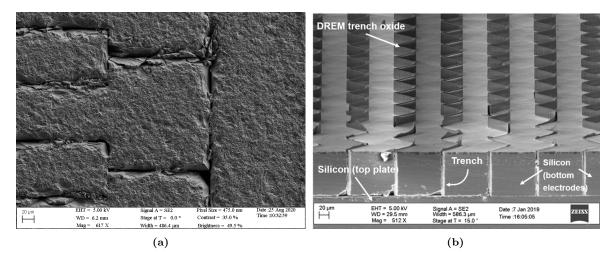

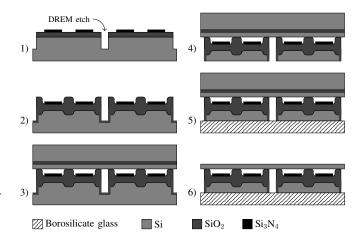

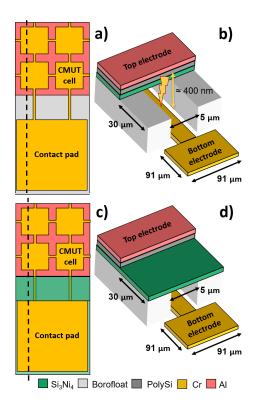

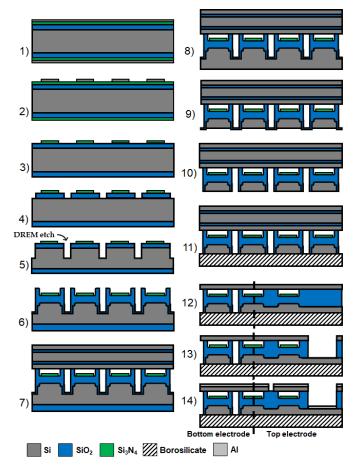

Figure 1.4: Cross-sectional view of five different RCA CMUT fabrication technologies. (a) Fusion bonding of a silicon top plate to a LOCOS structure grown on a doped SOI substrate. Figure is adapted from [64]. (b) Adhesive polymer bonding of a silicon nitride membrane to a fused silica wafer with metal electrodes using polymer [65]. (c) Sacrificial release method using a metal or doped silicon bottom electrode, where cavities are formed by etching of a sacrificial layer encapsulated in silicon nitride. (d) Anodic bonding of an insulated top plate to a structured borosilicate glass substrate with metal electrodes [55]. (e) A combination of a silicon top plate fusion bonded to a LOCOS structure and a borosilicate glass plate anodically bonded to the backside. A doped silicon substrate separated with a trench etch is utilised as bottom electrodes [1].

the cell cavities, and the substrate is bonded to a silicon top plate. This has a maximum processing temperature of  $375 \,^{\circ}\text{C}$  and can like (1)-(3) utilise a broad range of metals.

In contrast, CMUT top electrodes are typically made using a wafer-bonded plate of silicon or a membrane of silicon nitride, which is then covered with a thick metal layer of low resistivity. For typical electrode designs the electrode resistance of the top electrode will not affect the pressure field [69]. The metal deposition happens as one of the last process steps and is not affected by previous high temperature processes. It can therefore be used in combination with various types of CMUTs.

An ideal structure for low resistance signalling could be a glass wafer patterned with CMUT cells, using a relatively thick metal bottom electrode [28], [55], [57], such as the anodically bonded structure in Fig. 1.4(d). An alternative is the adhesions bonded device in Fig. 1.4(b). These types of devices will, if the plate or membrane collapses in one cell, short-circuit and possibly destroy the whole element if a protective dielectric layer is not used. The process of structuring cell cavities in a glass substrate with an etching process or by utilising a dielectric layer for the plate can, however, create stability issues and dielectric charging of the device [70]–[72]. Charging is a highly unwanted phenomenon which is currently not fully understood [73]. The effect can decrease the performance of the CMUT devices over time by opposing the electrical field inside the cells set up by an applied direct current (DC) bias voltage.

A fabrication process based on an SOI substrate together with the LOCOS technique [63] and fusion bonding have been shown to exhibit little to no charging [64]. The structure is illustrated in

Fig. 1.4(a). The LOCOS process, when used for CMUT fabrication, allows for reduced parasitic capacitance, high dielectric strength, good uniformity and tightly controllable CMUT dimensions and vacuum gap height down to under 10 nm precision due to the predictability of the oxide thickness [74]. Care should be taken to use an SOI wafer with a sufficiently thick device layer with a low resistivity to reduce the adverse attenuation in the bottom electrodes. The fusion bonding process is, however, very sensitive to particles present on the wafer surface during bonding on the top plate to the bottom substrate, and the surfaces need a very low RMS roughness of  $\leq 0.5$  nm to 1.0 nm [28], [75], [76]. There is therefore a high risk of a reduced array yield through the fabrication process. This problem will quickly scale with large RCA arrays as the defect free surface area needed scales with the number of elements.

The anodic bonding process is in comparison far less sensitive to particles caught between the wafers during bonding [77] and this can be a tremendous factor in increasing yield for large RCA arrays.

The two methods of fabricating bottom electrodes for CMUTs with highly doped silicon and metal electrodes are explored in this PhD thesis.

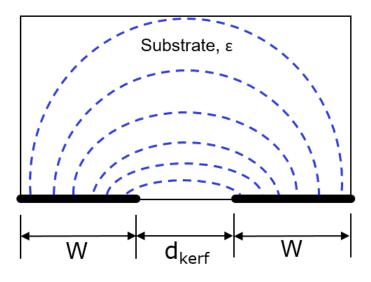

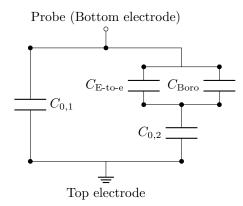

#### 1.4.2 Substrate coupling

Another important consideration or criterion is that the receive sensitivity of both rows and columns should be equal to ensure even performance. The sensitivity will depend on how well the substrate coupling or cross-talk between elements [78] can be suppressed. The performance of each element in regards to the signal attenuation caused by the electrode resistance will likely also have an affect on the sensitivity. CMUT elements which are fabricated with a silicon substrate often utilise an SOI wafer during fabrication with an insulating layer to separate bottom electrodes from the handling substrate [47], [52], [64], [79]. This allows the elements to capacitively couple to each other through the substrate, giving rise to parasitic capacitance which will lower the receive sensitivity of the array as explained in [78]. This effect is primarily seen for the bottom electrodes integrated directly on top of the SOI or silicon substrate. By utilising only the columns (bottom electrodes) for transmitting and rows (top electrodes) for receiving, this problem can be reduced but will prevent complex transmit and receive sequences using both rows and columns.

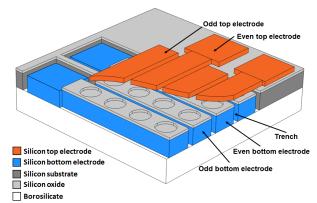

A way to mitigate coupling effect could be to increase the signal path length between the elements by partially separating them with an etching process [69]. In this way the  $\omega RC$  product is utilised by providing a high resistance path vertically in the elements, thereby attenuating the signal propagating through the substrate to the neighbouring element. To preserve a low  $\omega RC$  along the elements, a highly-doped silicon electrode is needed. An alternative solution could be removing the electrical path through the substrate completely, which has previously been demonstrated in this group [65], [80]. If for example, a silicon device layer is used as bottom electrode, the elements can be completely separated by a deep silicon etching process and an insulating glass substrate can be bonded to the backside as an alternative to silicon. This structure is shown in Fig. 1.4(e) as a combination of a conventional, to this group, LOCOS based process, which is combined with deep trench etch and bonded to an insulating borosilicate glass substrate [1].

#### 1.5 The super resolution imaging project

This PhD project is part of the Super Resolution Imaging (SRI) project supported by Innovationsfonden. The SRI project is a collaboration between DTU Health Technology, Rigshospitalet, KU and the company BK Medical. By combining the strengths of the partners, DTU will be able to make a significant contribution to the field of 3D super resolution ultrasound imaging. The PhD project is centrally located within the strategy of DTU Health Tech, with a focus on medical components, materials development, transducers and new technology. The project combines micro and nanotechnology for development of ultrasonic transducers. Recent results show that this opens up new possibilities for design of ultrasonic scanner probes suitable for 3D super resolution imaging. Thus, the scientific hypotheses are clear and well-defined. The project is highly innovative and the results will, in addition to publication in international journals, be used to develop a new generation of ultrasound scanner probes having integrated microfabricated 2D transducer arrays which will enable 3D super resolution visualization.

The main idea of the project is built on the concept of super resolution, which relies on imaging objects smaller than the diffraction limit of the wavelength used. By definition, objects below the limit cannot be resolved with conventional methods and will appear blurred and highly distorted by the point spread function of the imaging system. The spatial position of the sub-wavelength objects can instead be estimated by center of mass calculations. This principle can be used for super resolution imaging using ultrasound by injection gas micro-bubbles into the blood stream. Since the acoustical impedance of the bubbles is higher than the surrounding blood and tissue, a large ultrasonic echo is received. This can be used to accurately localise the sub-wavelength bubbles for super resolution imaging. This was previously demonstrated in 2D imaging using 1D probes [81]. However, in in-vivo experiments in the blood vessels the bubbles will occasionally move out of the 2D imaging plane as they are not confined in a single plane, but instead spread out in three-dimensional space. By utilising 2D ultrasonic transducer arrays, producing 3D volumetric images, the bubbles can be accurately tracked in blood steam. If the signals contributed from all the tracked bubbles are combined, a 3D map of the vascular network of organs can be generated and used for diagnostic imaging of vascular diseases and for spotting the onset of malicious tumours.

#### 1.6 This PhD project

In this thesis is presented the culmination of the research, design processing, fabrication, and characterisation performed in this PhD project.

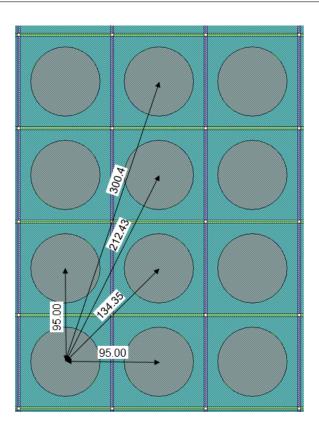

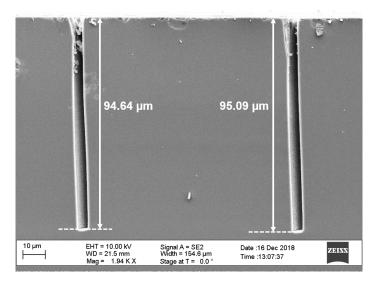

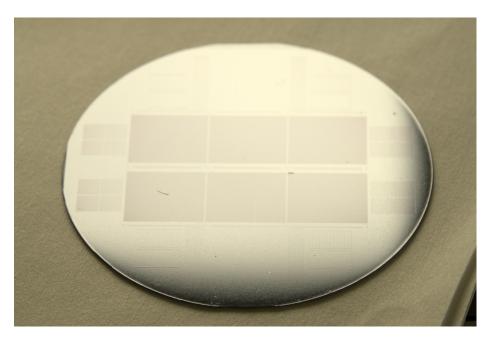

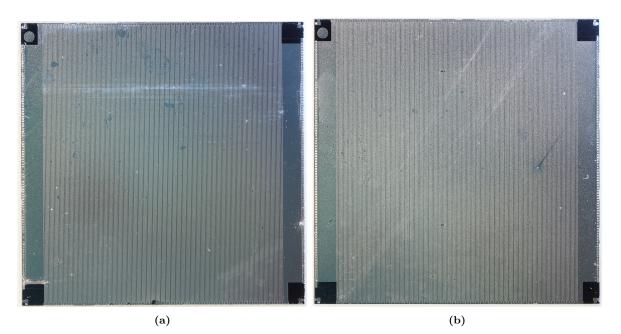

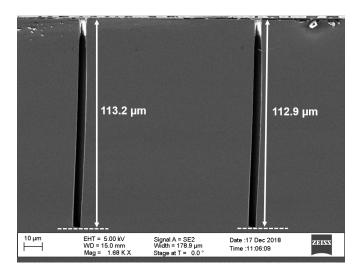

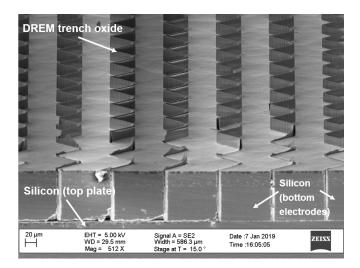

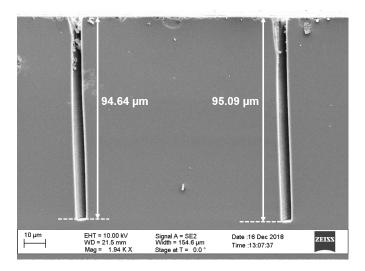

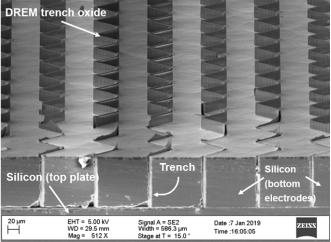

This PhD project thesis is split into two parts. In Part I a hand-held RCA CMUT based probe for volumetric imaging with a potential use in medical applications is treated in detail. This probe uses a generation of RCA CMUT chips called *transducer rodent 2* (TR2) based on a previous *transducer rodent 1* (TR1) chip, presented in the PhD thesis by Andreas Spandet Havreland [82]. These chips mounted in the probe were meant to be used for clinical pre-trials on rats before later clinical trials are to be performed on humans, using either this probe or another generation of chips. This device is based on a LOCOS process fabricated on a doped silicon wafer. The elements are made in a combination with fusion bonding to an SOI wafer and a physical separation of the bottom electrodes to reduce cross-talk between the elements, which was presented by the author in [80]. This is realised using a deep reactive-ion etching (RIE) based process. For improved mechanical stability, while also providing element-to-element insulation and low capacitive substrate coupling, a borofloat glass wafer is anodically bonded to the backside of the elements after the separation process. The separated electrodes have a cross-section of almost  $100 \times 100 \,\mu\text{m}^2$  which combined with a highly doped silicon substrate will mitigate delay-line effects.

The various aspects of the probe development, e.g. the chip design and fabrication, the probe electronics and probe handle and the imaging techniques, was done in a collaboration between the company BK Medical ApS and their ultrasound probe development department and the research groups at DTU: the Center for Fast Ultrasound Imaging (CFU) and the MEMS-Applied Sensors group at DTU Health Technology, which the author of this thesis is a part of. The fusion-anodic double bonded structure is illustrated in Fig. 1.4(e) and as a cross-sectioned 3D sketch in Fig. 1.5. This device should benefit from stable high-performing CMUTs while also exhibiting low element-to-element coupling and high transmit pressure uniformity.

In Part II a hand-held RCA CMUT based prototype probe is presented and the design, development, fabrication and characterisation of the *transducer human 1* (TH1) generation of RCA CMUT chips are treated in detail. The design of these are based on previous anodically bonded arrays from the PhD projects of Mathias Engholm [83] and Andreas Spandet Havreland [82] and the Masters'

**Figure 1.5:** A 3D sketch of the corner of an RCA array made using the fusion-anodic double bonded method. The orthogonal blue bottom electrodes and orange top electrodes, made of silicon, are shown encapsulating the structured oxide layer with the circular CMUT cells. A wide trench is shown separating the bottom electrodes laterally, and a glass substrate (borosilicate) is shown bonded to the backside of the structure.

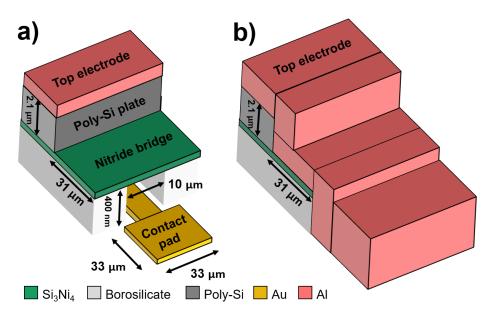

projects by Kitty Steenberg [84] and Magnus Galsgård Petersen [85]. The anodic bonded structure is illustrated in Fig. 1.4(d) and a previously fabricated structure is presented in [55]. This device uses a substrate made of borosilicate glass to reduce substrate coupling or cross-talk between the elements. The top electrode and plate will be made of poly-silicon covered by aluminium, and will be insulated from short circuits in the cell cavities with a silicon nitride layer, as illustrated in Fig. 1.4(d). The bottom electrodes will be made of metal which will mitigate delay-line effects. In [55] an improvement to the design is made, which makes it possible to reliably perform wafer level characterisation on the arrays in air without the need for insulating encapsulation material. This is done by extending the silicon layer to the edge of the bottom electrode contact pad.

This TH1 chip in the prototype probe is made in collaboration with the same partners in the SRI project and was also meant to be used first for clinical pre-trials on rats before later clinical trials are to be performed on humans.

#### 1.7 Publications

This thesis is partly based on the following publications of which the author is either a main or co-author. These publications are: four IEEE IUS conference proceedings and one journal article published in special issue on micromachined ultrasonic transducers in the IEEE OJUFFC.

- Paper A Rune Sixten Grass, Andreas Spandet Havreland, Mathias Engholm, Jørgen Arendt Jensen and Erik Vilain Thomsen, "188+188 Row-Column Addressed CMUT Transducer for Super Resolution Imaging," in Proc. IEEE Ultrason. Symp., IEEE, 2019, pp. 746–749.

- Paper B Erik Vilain Thomsen, Kitty Steenberg, Magnus Galsgård Petersen, Mads Weile, Andreas Havreland, Martin Lind Ommen, Rune Sixten Grass, and Mathias Engholm., "Wafer Level Characterization of Row-Column Addressed CMUT Arrays," in *Proc. IEEE Ultrason. Symp.*, IEEE, 2019, pp. 770-773.

- Paper C Andreas S. Havreland, Mathias Engholm, Rune S. Grass, Jørgen A. Jensen, and Erik V. Thomsen. Wafer bonded CMUT technology utilizing a poly-silicon-on-insulator wafer. In Proc. IEEE Ultrason. Symp., pages 758–761. IEEE, 2019.

- Paper D Rune Sixten Grass, Kitty Steenberg, Andreas Spandet Havreland, Mathias Engholm and Erik Vilain Thomsen, "Large Scale High Voltage 192+192 Row-Column Addressed CMUTs Made with Anodic Bonding," in Proc. IEEE Ultrason. Symp., IEEE, 2020, pp. 1–4.

- Paper E R. S. Grass, M. Engholm, A. S. Havreland, C. Beers, M. L. Ommen, S. L. G. Pedersen, L. N. Moesner, M. B. Stuart, M. T. Bhatti, B. G. Tomov, J. A. Jensen, and E. V. Thomsen, "A Hand-Held 190+190 Row-Column Addressed CMUT Probe for Volumetric Imaging," Submitted for review in IEEE Open J. Ultrason., Ferroelec., Freq. Contr. in a special edition on micromachined ultrasonic transducers, 2022.

#### 1.8 Thesis outline

This thesis is divided into three introductory chapters, followed by two parts detailing the design, fabrication, assembly and electrical and acoustical characterisation of two TR2 and TH1 probes. The two parts each consist of three chapters consists. Finally a conclusion is given.

A description of each chapter is given

- Chapter 1 Introduction This chapter provides an introduction to the background of medical ultrasound imaging and a few of the different modalities used when scanning patients. An introduction the the CMUT as a platform for ultrasound imaging is given together with a brief literature study and a view into the state-of-the-art of arrays and probes. The benefits of using 2D CMUT row-column arrays for 3D imaging are discussed. Furthermore, criteria for large CMUT arrays regarding the electrode resistance and substrate coupling in relation to the choice of bottom electrode material are discussed. The CMUT designs chosen for this PhD thesis are then justified and details of the research project is given. These two designs are; 1) a LOCOS based CMUT design, which combines highly doped silicon electrodes with low resistivity, a fusion bonding process for cell encapsulation and an anodically bonded glass substrate for reduced capacitive substrate coupling. 2) a glass based substrate with etched CMUT cavities, using anodic bonding for cell encapsulation, and metal electrodes with low resistivity.

- **Chapter 2 CMUT RC design** This chapter presents a method for designing CMUT devices using a combination of analytical expressions and simulations using finite element method (FEM) software. Starting from the desired center frequency of the CMUT device in immersion, the element pitch, cell geometry, center frequency in vacuum, and electrical parameters used in operation can be modelled. The predicted signal attenuation of long elements can also be evaluated based on the electrode resistance and the value of the dimensionless  $\omega RC$  product, and can used be used in an iterative design process to optimise electrical and acoustical performance.

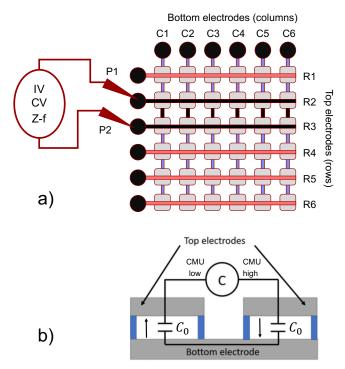

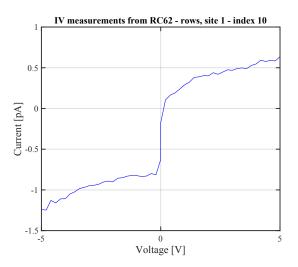

- **Chapter 3 Wafer level characterisation** This chapter shows the methodology of the various electrical tests performed on CMUT arrays using an automatic wafer probing station. The purpose of each test in the performance evaluation of the array is described.

#### Part 1 - LOCOS-based CMUTs - Transducer Rodent 2 (TR2)

This part treats the development of the Transducer Rodent 2 (TR2) probe

**Chapter 4 - Design** In this chapter the TR2 CMUT design considerations are presented. These are based on the CMUT RC design method in Chapter 2. The geometry of the CMUT cell and center frequency were determined from the center frequency in immersion. The Bragg and substrate ringing frequencies were found and the estimated signal attenuation of the transmitting elements were calculated based on the  $\omega RC$  product. Changes to the design were briefly discussed and the array and wafer layout presented.

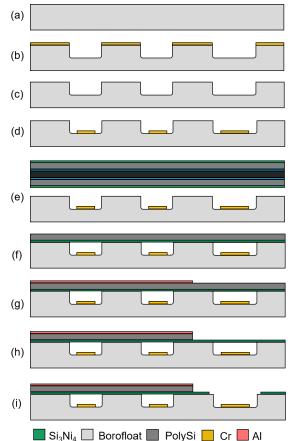

- **Chapter 5 Fabrication** This chapter provides a detailed overview of the fabrication process for the TR2 chip and its main steps. Various process recipes and parameters are listed for each step. The fusion and anodic bonding processes and their mechanisms are briefly discussed.

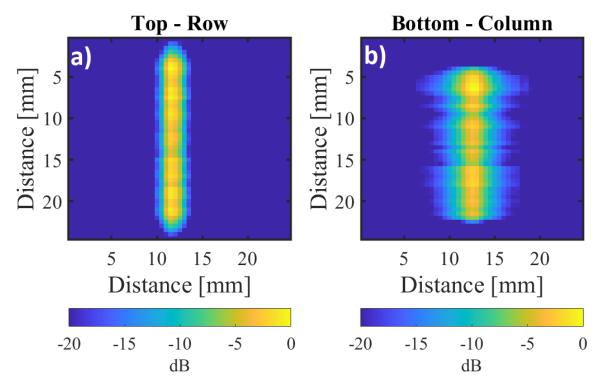

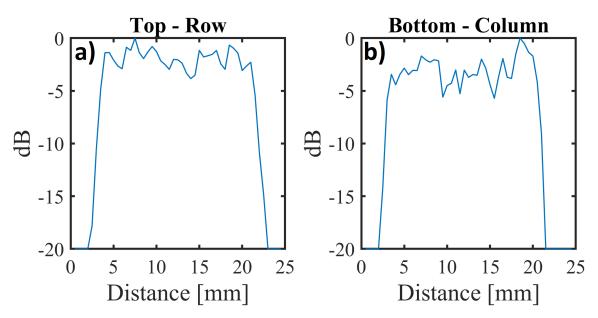

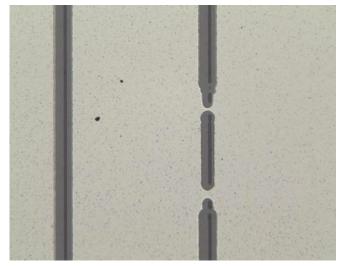

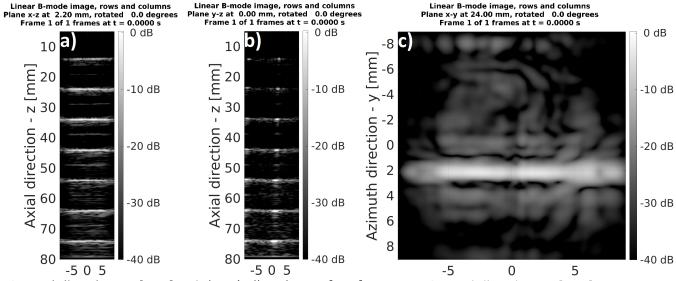

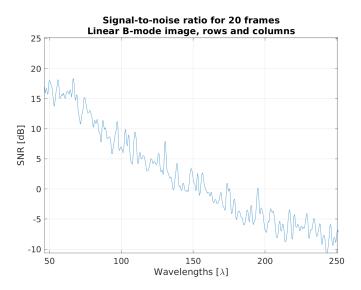

- **Chapter 6 Transducer characterisation** The chapter describes the characterisation of the TR2 chip and probe. The fabricated TR2 chip is first electrically characterised before it is mounted in the probe handle. This involves impedance measurements and pull-in tests. The probe assembly process is described and details are provided when available. Then the performance of the probe is evaluated by acoustical characterisation. This involves performing measurements in transmit, by receiving the probe signal with a hydrophone, and in pulse-echo, by using the probe in both transmit and receive with a reflector plate. A short thermal characterisation of the probe is also given. In addition the 3D volumetric capabilities and resolution of the probe is evaluated by scanning on three different phantoms.

#### Part 2 - Anodic bonding based CMUTs - Transducer Human 1 (TH1)

This part treats the development of the Transducers Human 1 (TH1) probe

- **Chapter 7 Design** In this chapter the TH1 CMUT design consideration are presented. Specifically the TH1-A array generation is presented. An iteration of the TH1-A design, based on its fabrication results, called the TH1-B design, is included in Appendix A. The design process is based on the CMUT RC design method in Chapter 2. The geometry of the CMUT cell and center frequency were determined from the center frequency in immersion. The Bragg and substrate ringing frequencies were found and the estimated signal attenuation of the transmitting elements were calculated based on the  $\omega RC$  product. Changes to the design were briefly discussed and the array and wafer layout presented.

- **Chapter 8 Fabrication** This chapter provides a detailed overview of the fabrication process of the TH1-A chip and its main steps. Various process recipes and parameters are given for each step. A list summarising which processes that need optimisation is presented. Some of these have been implemented in the fabrication of the TH1-B chip described in Section A.2.

- **Chapter 9 Transducer characterisation** The chapter describes the characterisation of the TH1 chip and the prototype probe. The fabricated TH1 chip is first electrically characterised before it is mounted in the probe handle. This involves, IV, CV, and impedance measurements and pull-in tests. The probe assembly process is described and details are provided when available. Then the performance of the probe is evaluated by acoustical characterisation. This involves performing measurements in transmit, by receiving the probe signal with a hydrophone, and in pulse-echo, by using the probe in both transmit and receive with a reflector plate.

- **Chapter 10 Conclusion and outlook** An overall conclusion is given, summarising some of the important results of the development of the two large row-column probes and the challenges lying ahead.

### Chapter 2

# CMUT RC design

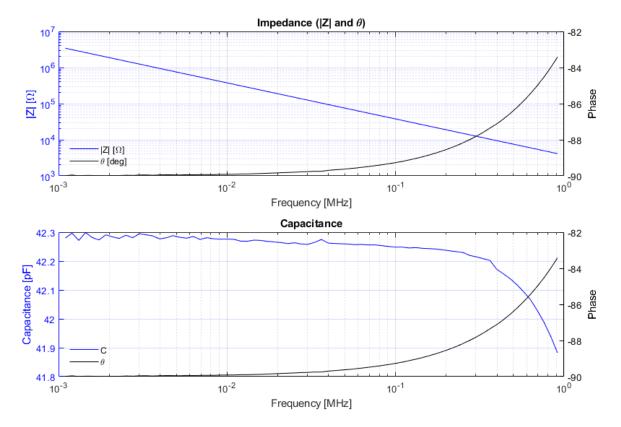

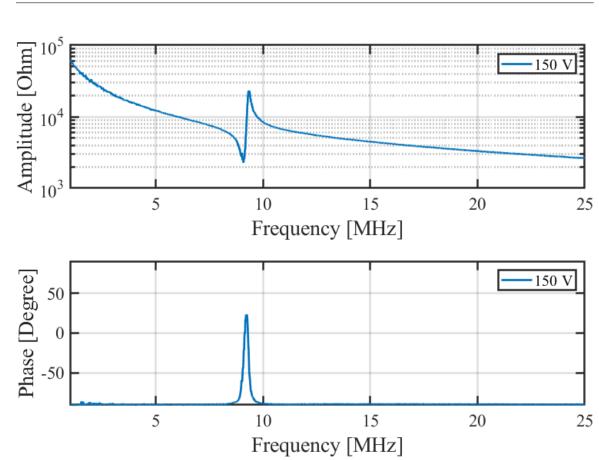

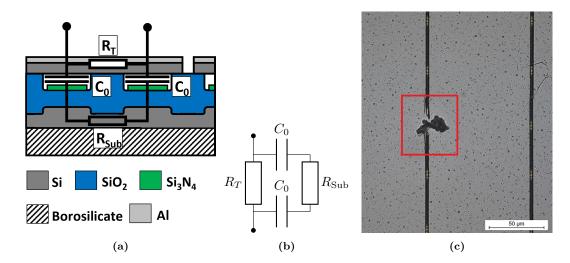

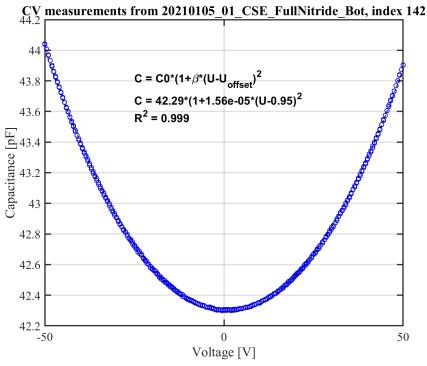

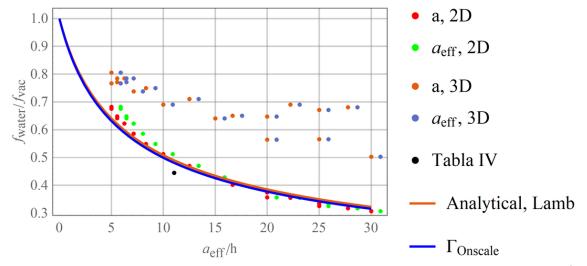

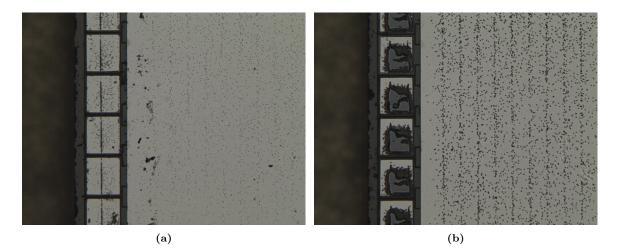

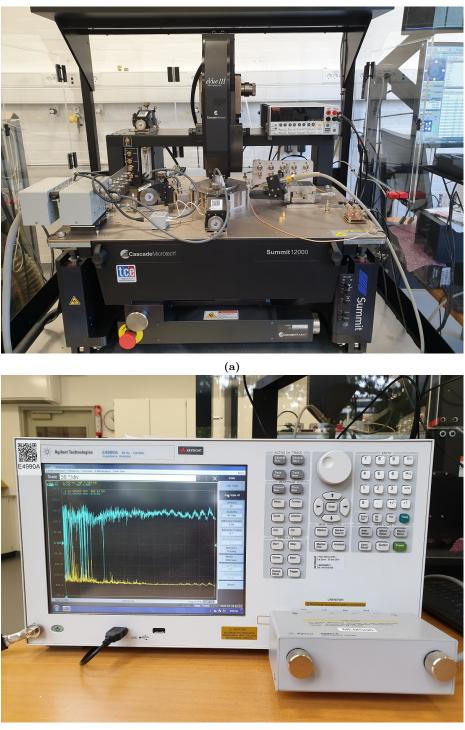

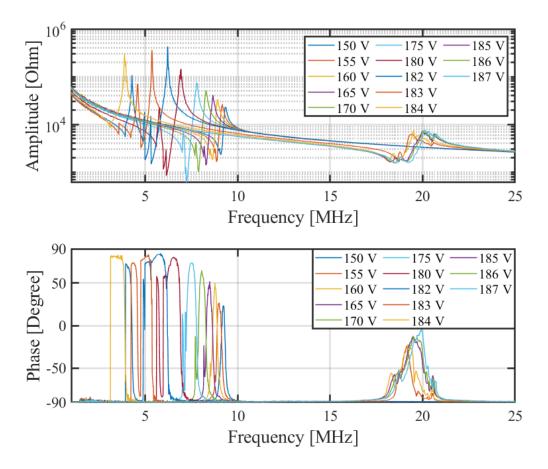

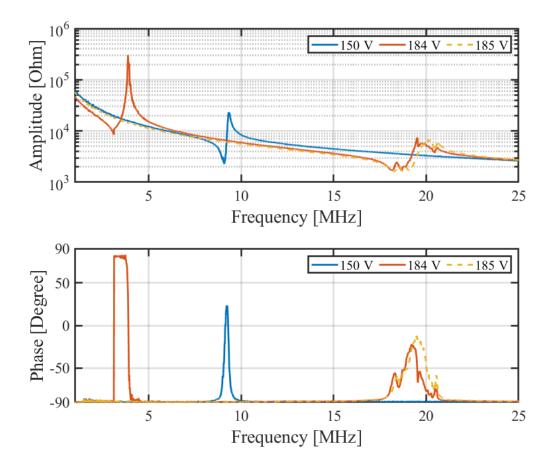

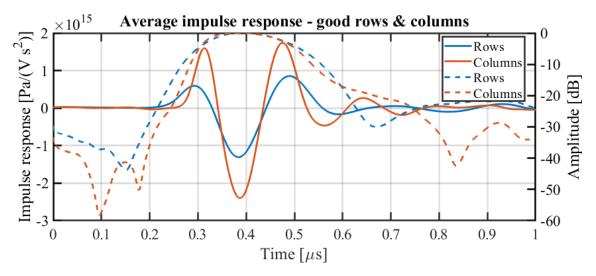

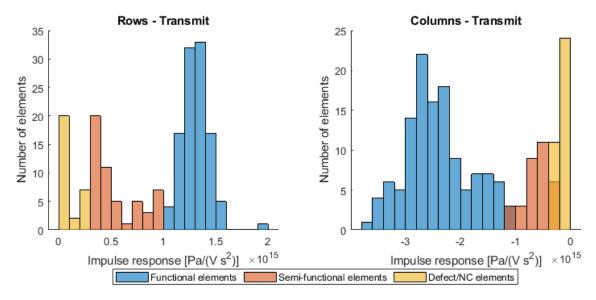

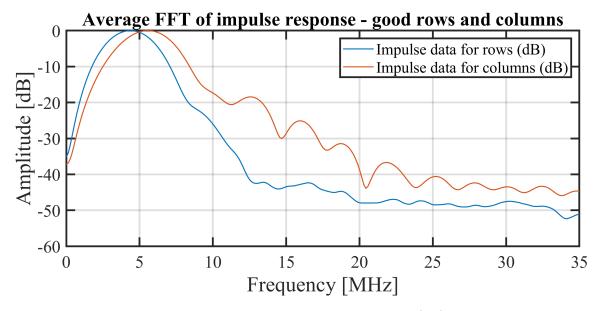

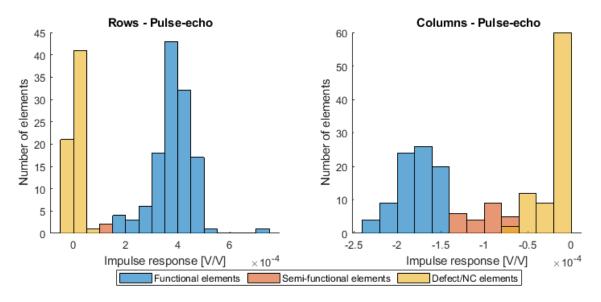

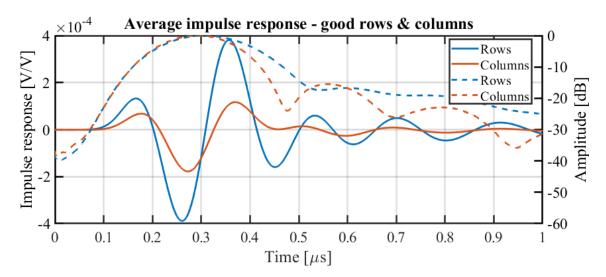

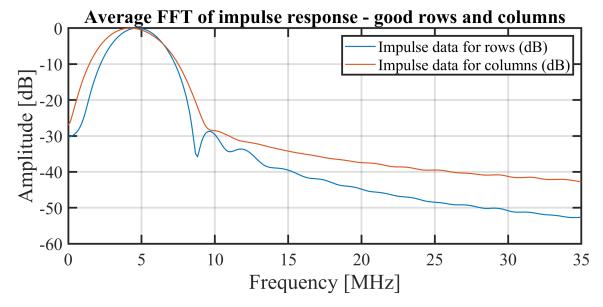

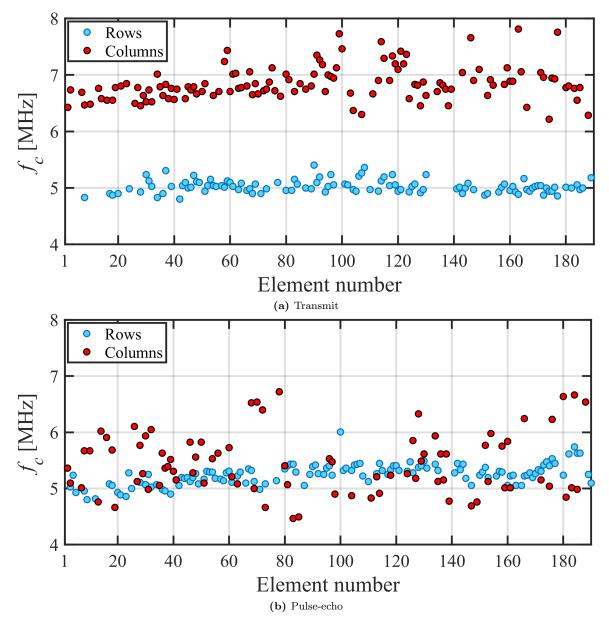

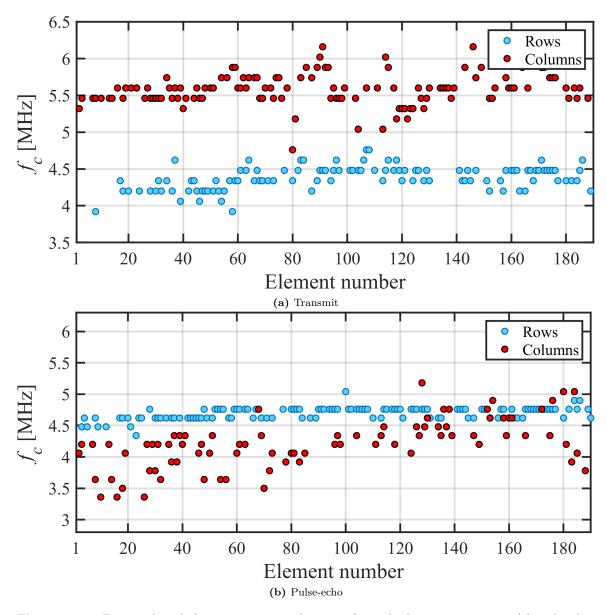

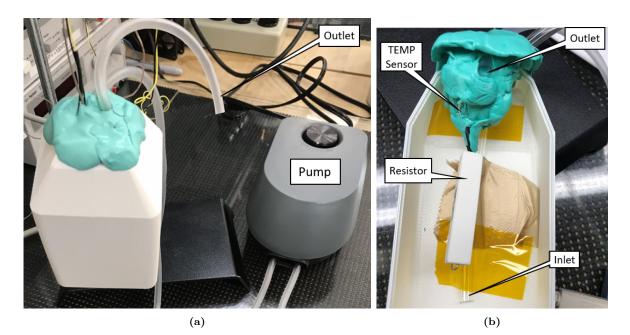

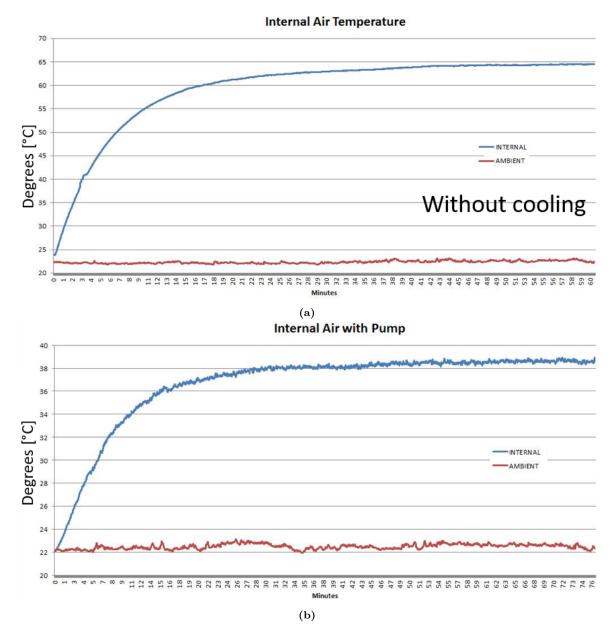

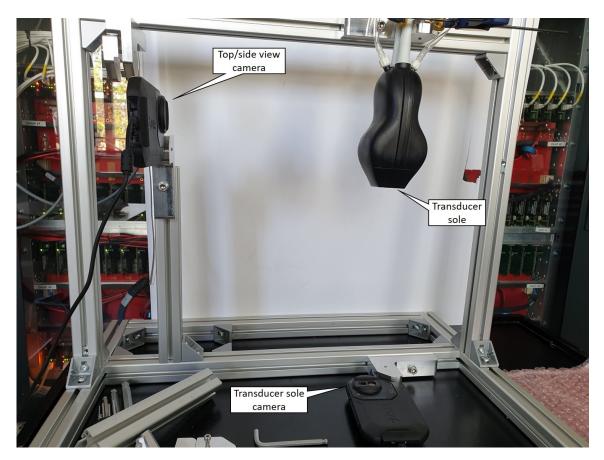

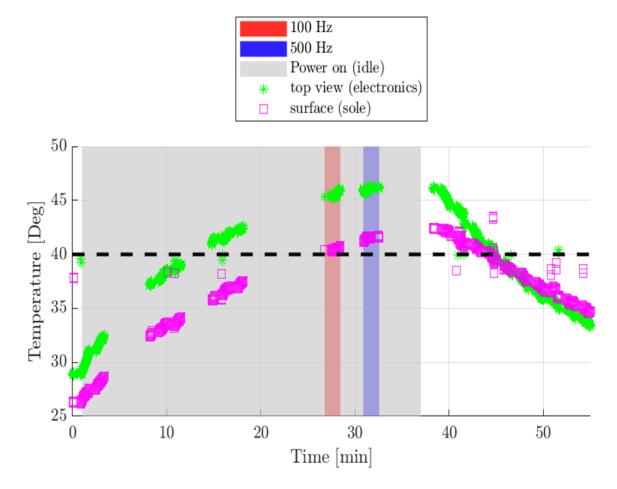

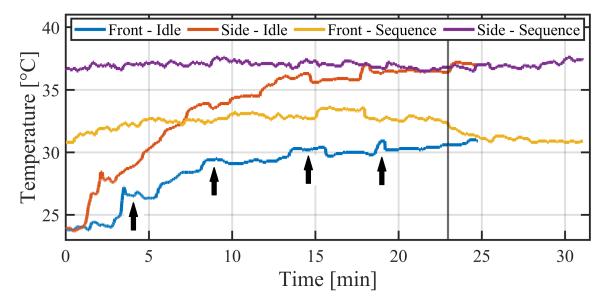

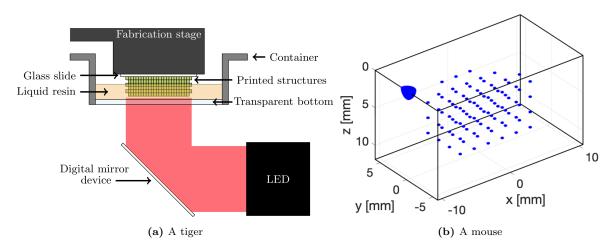

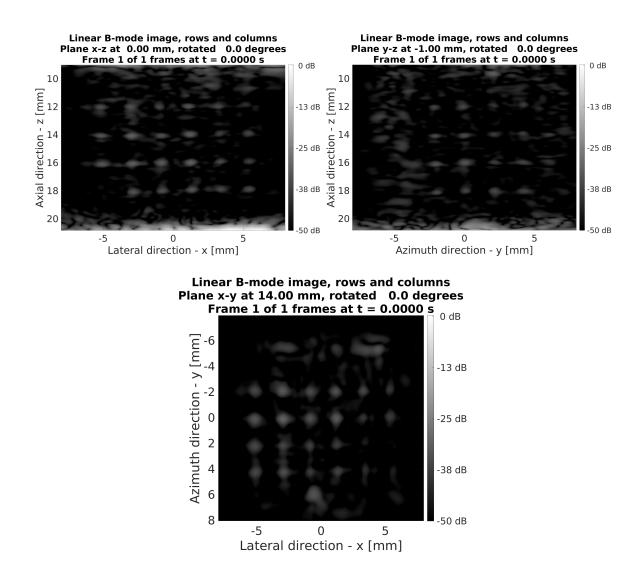

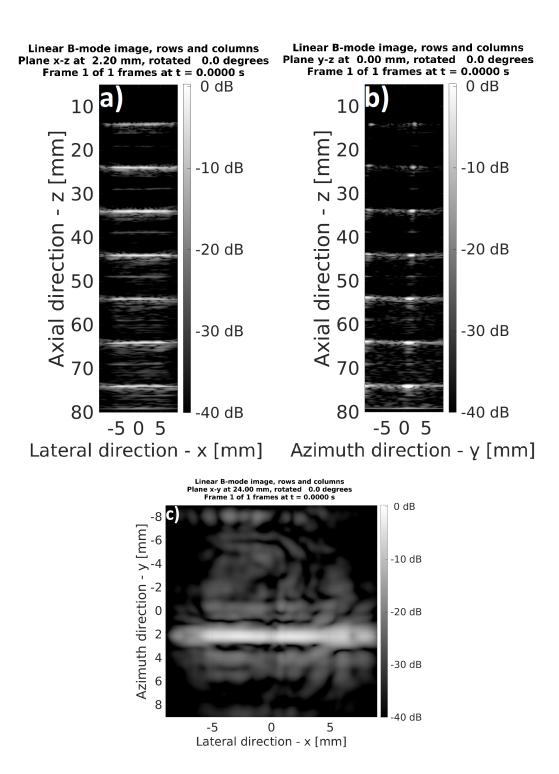

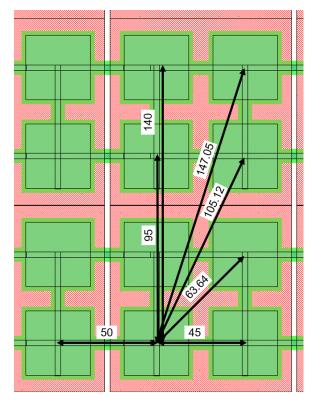

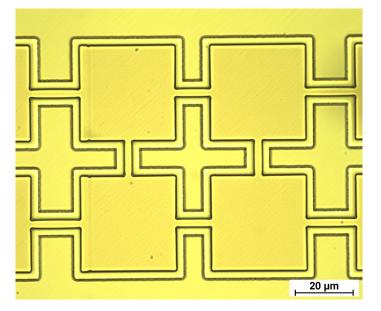

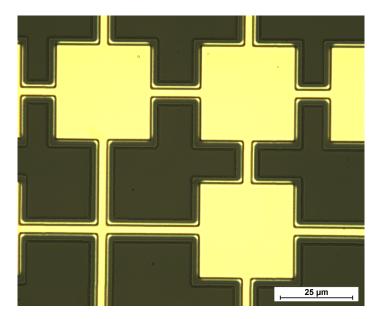

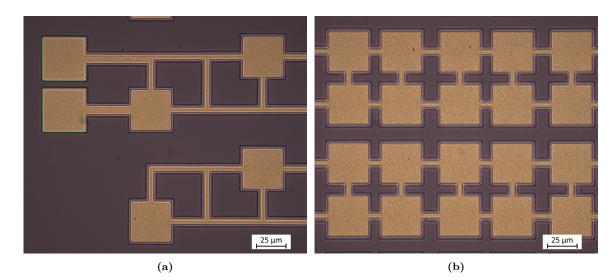

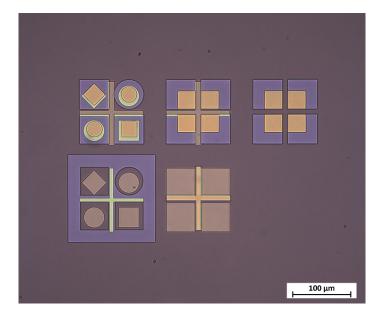

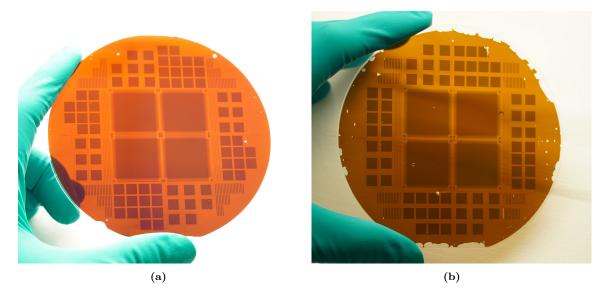

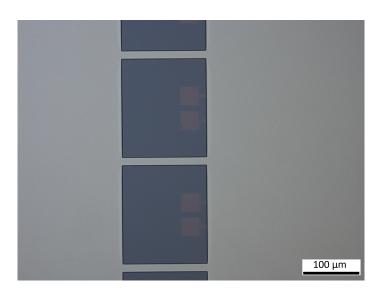

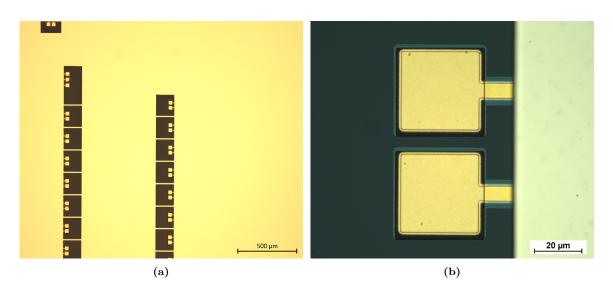

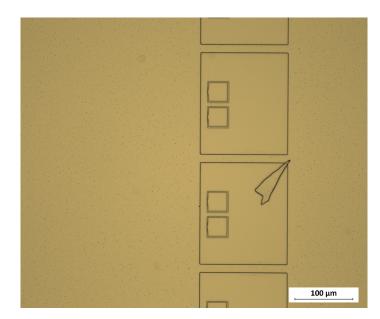

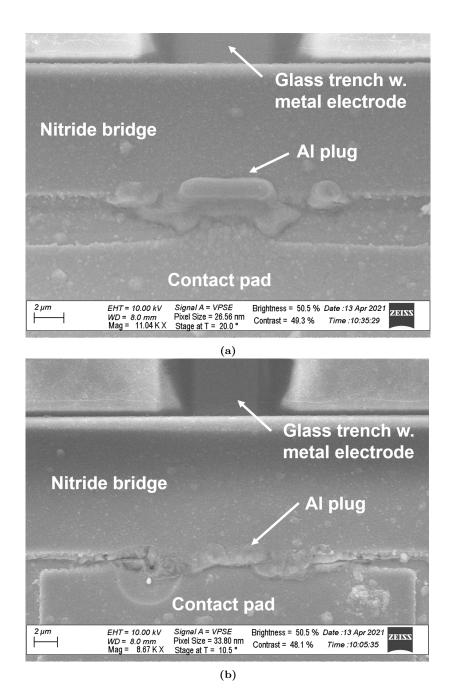

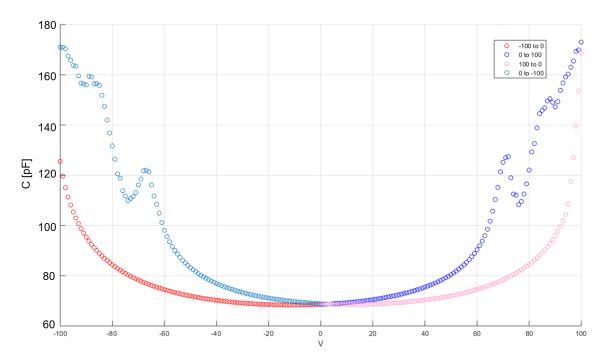

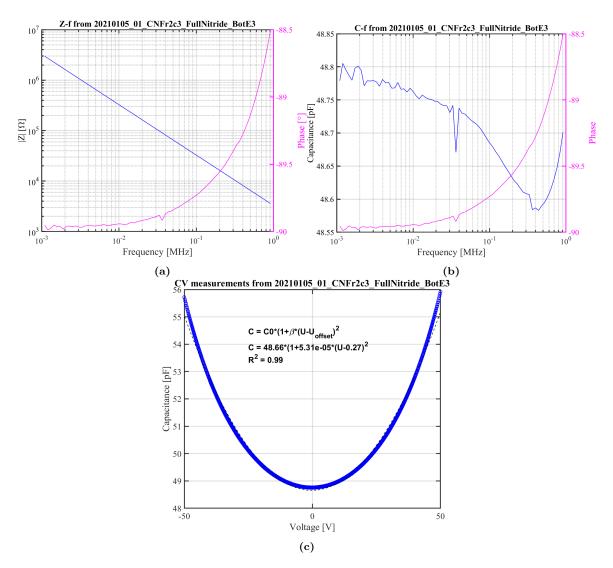

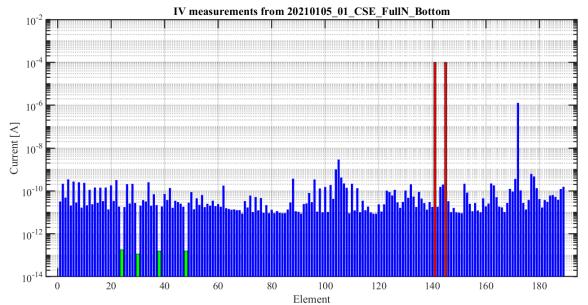

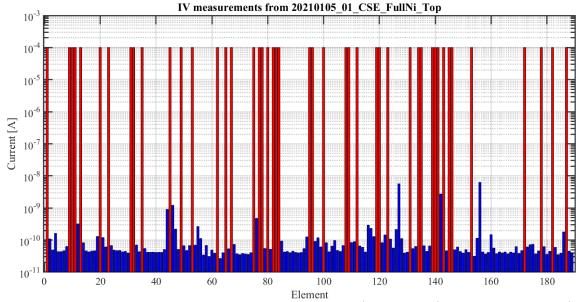

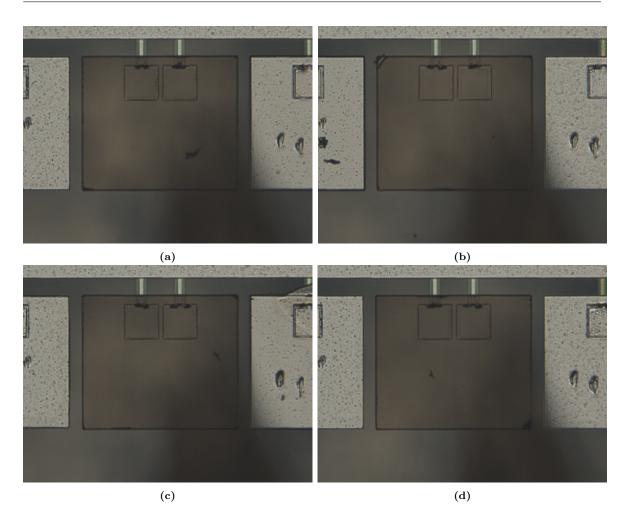

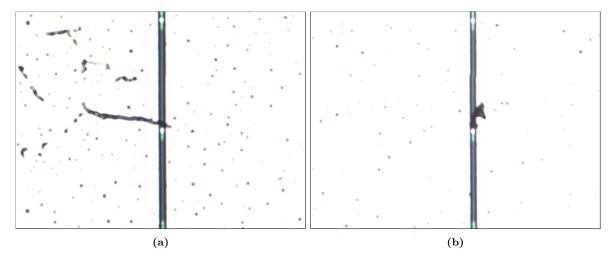

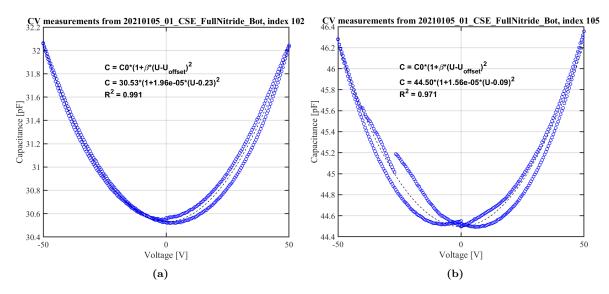

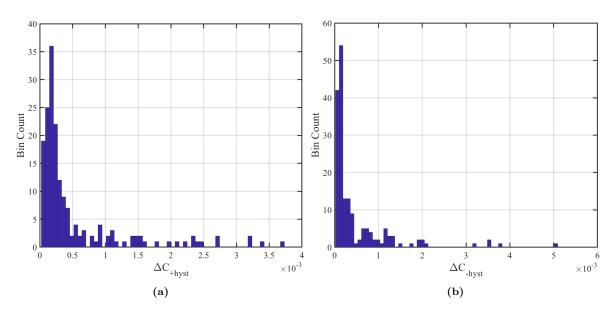

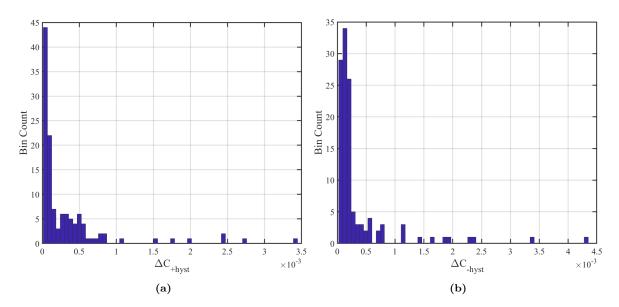

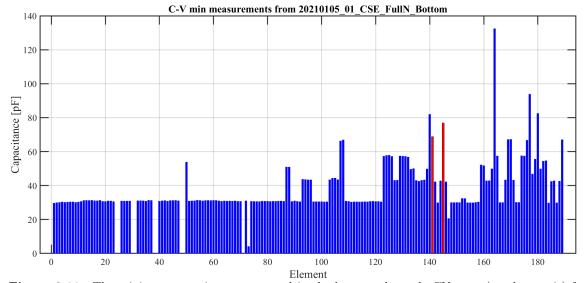

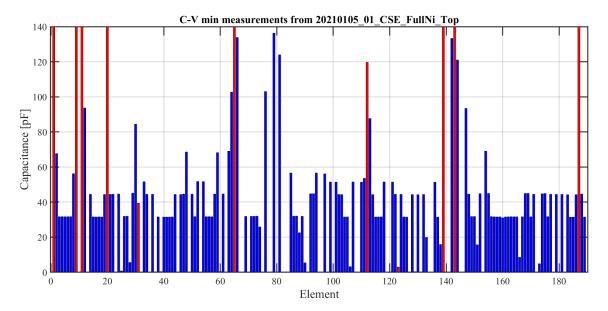

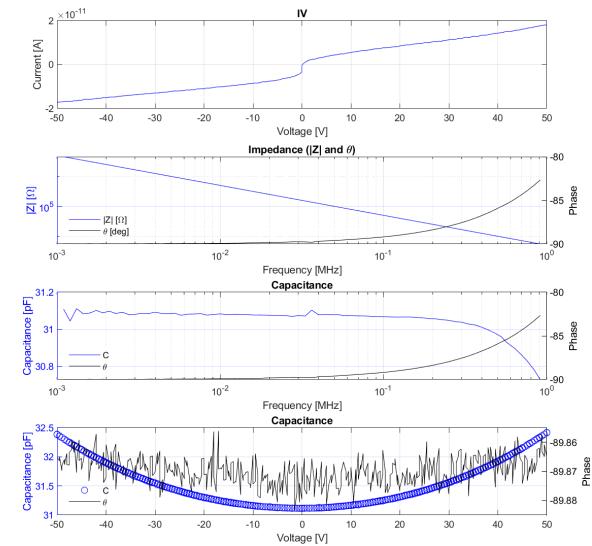

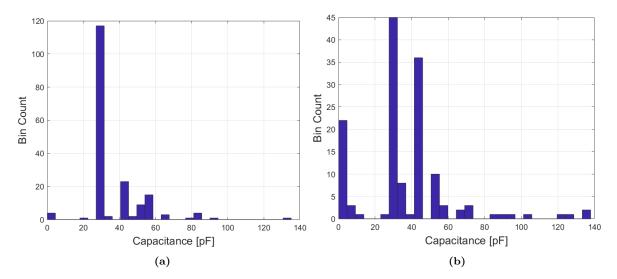

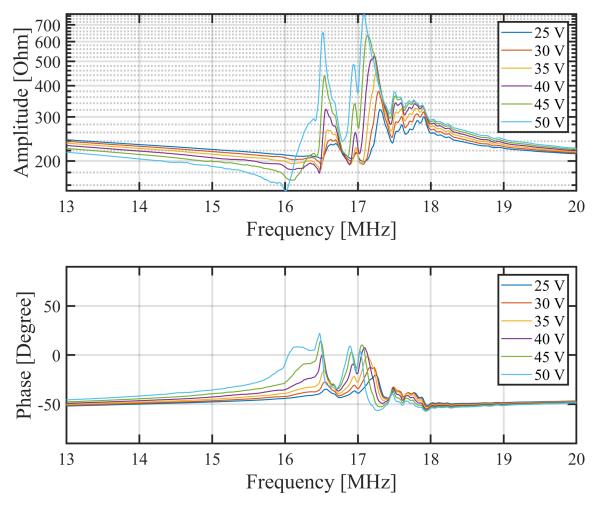

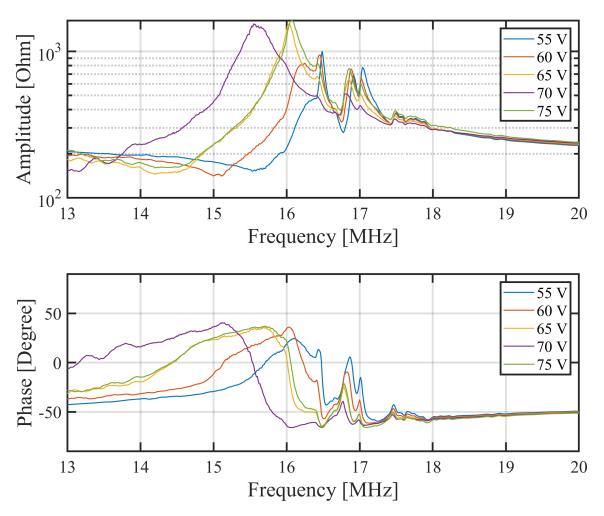

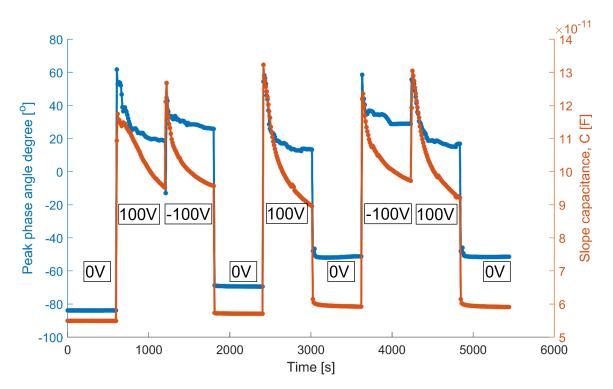

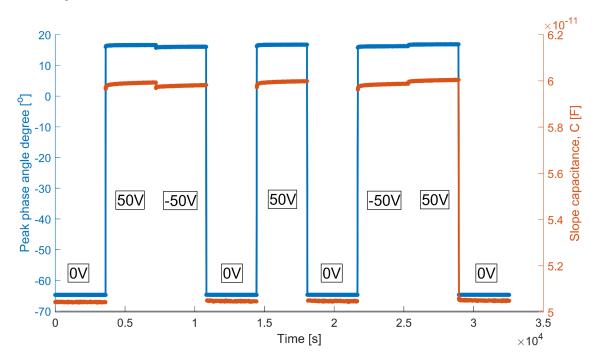

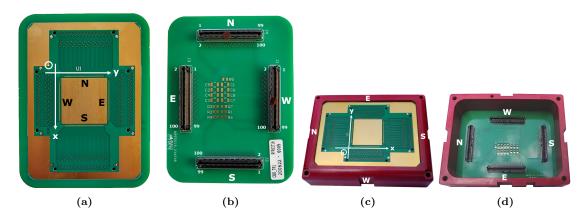

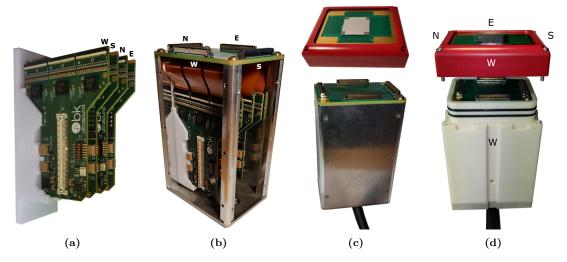

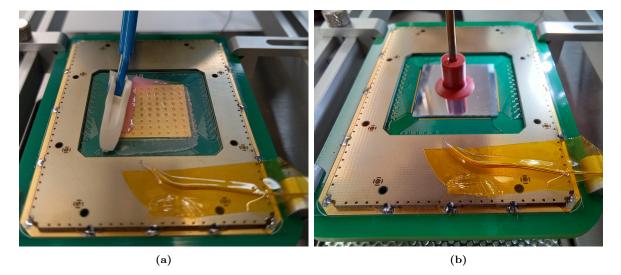

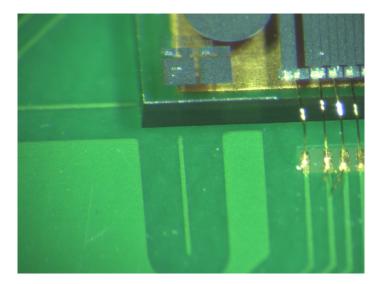

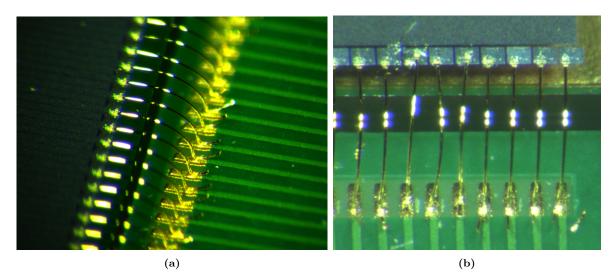

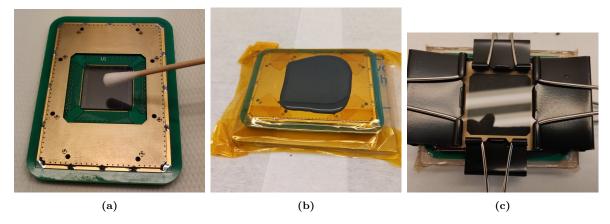

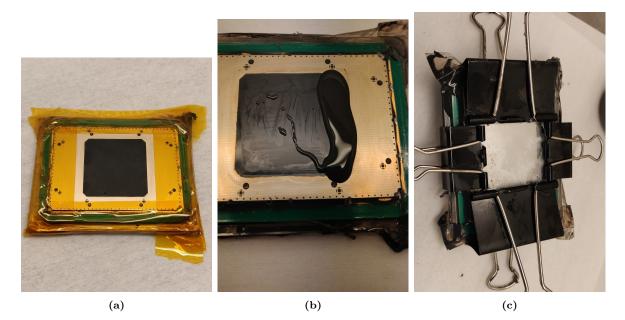

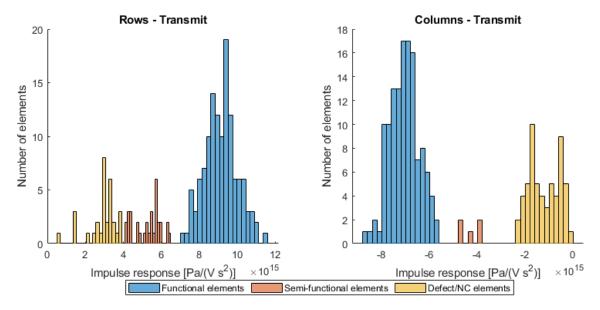

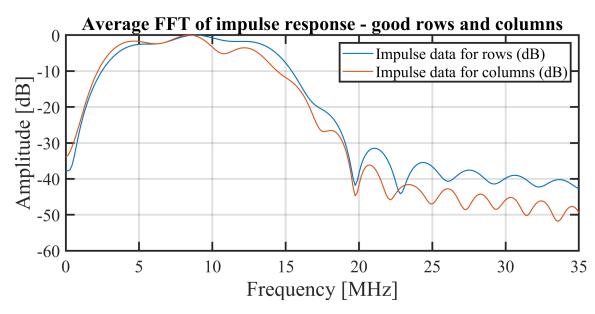

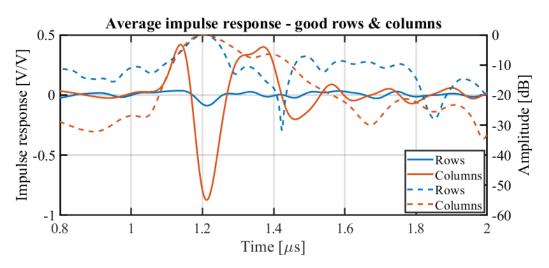

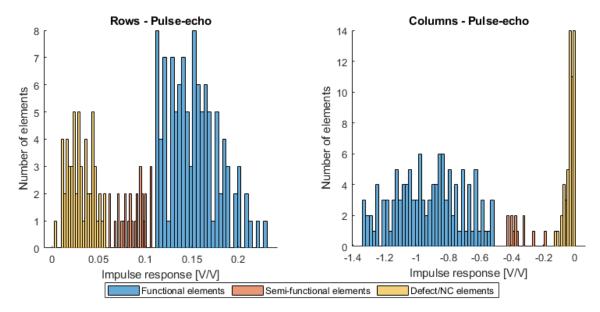

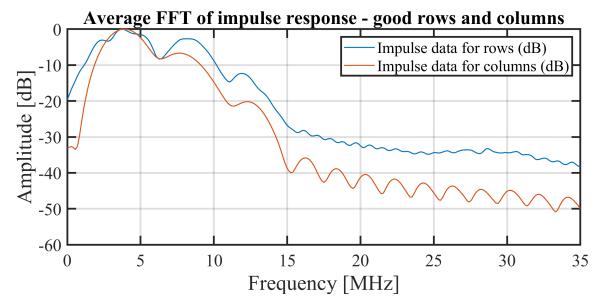

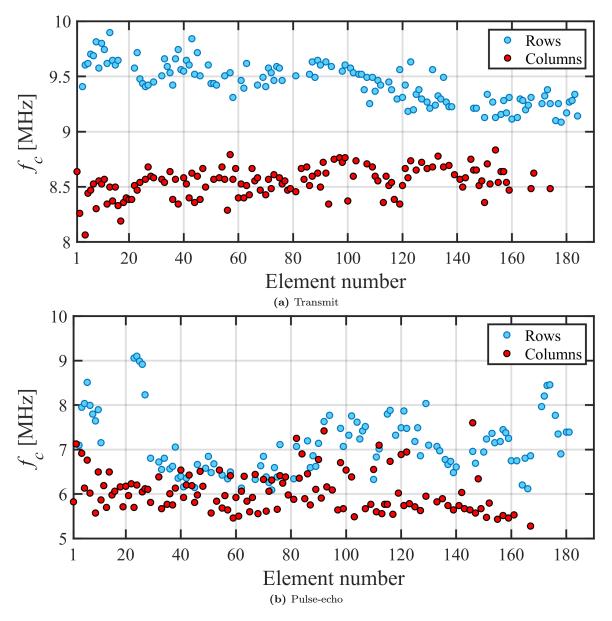

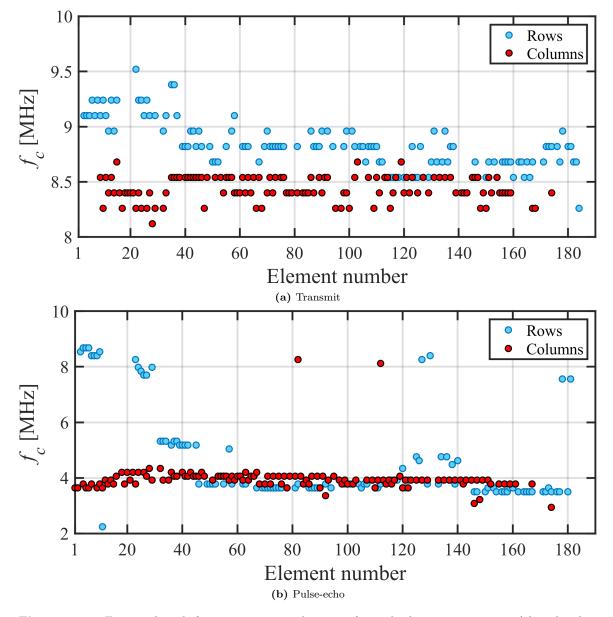

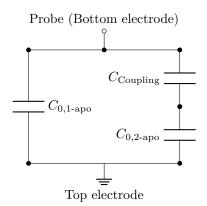

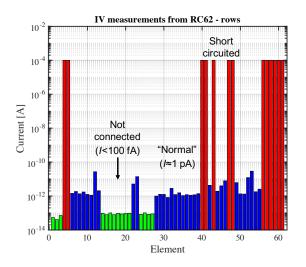

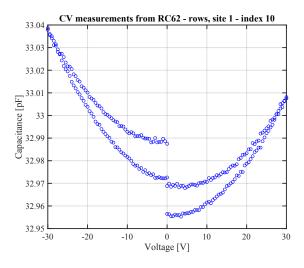

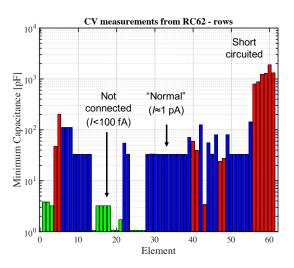

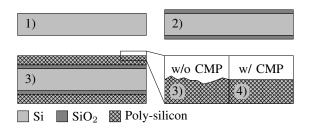

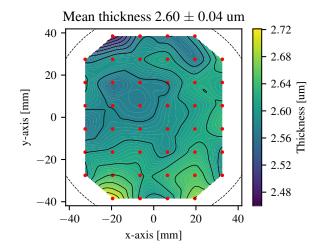

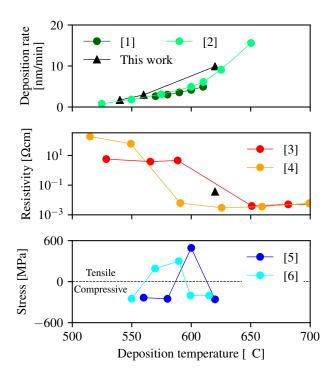

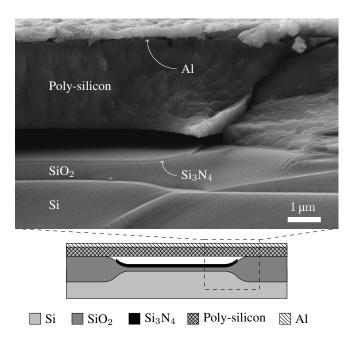

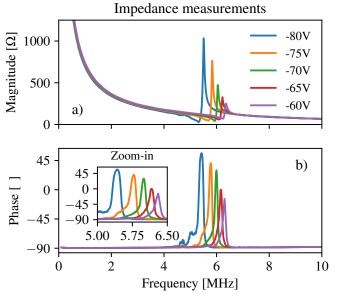

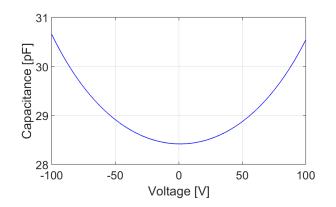

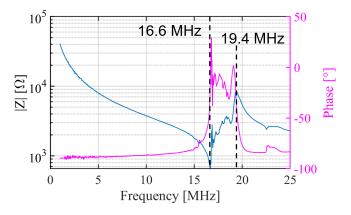

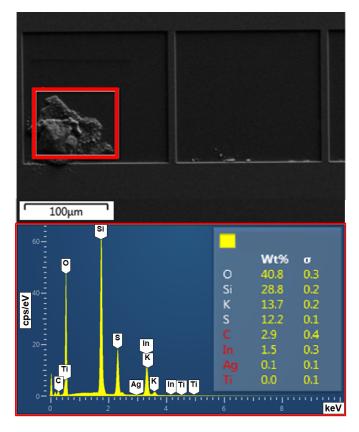

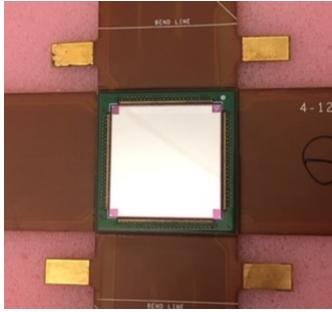

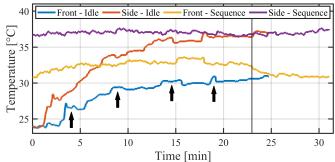

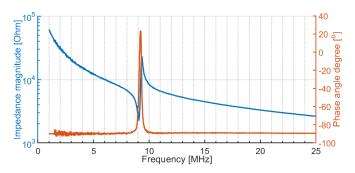

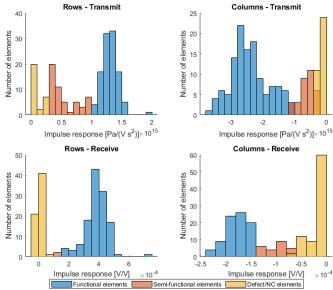

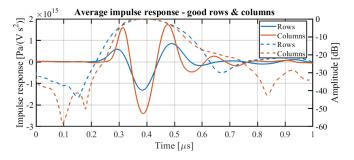

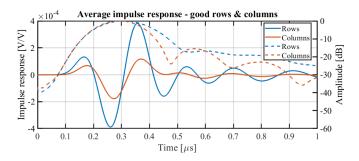

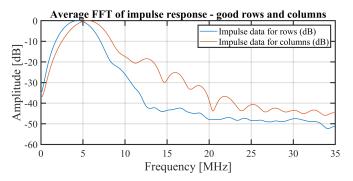

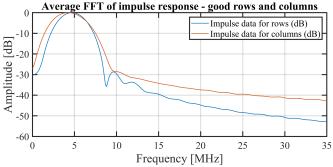

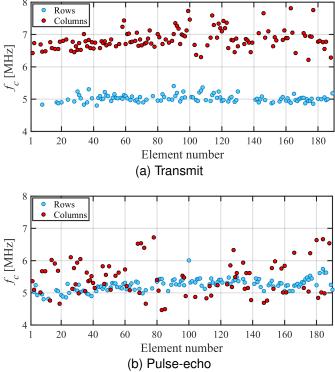

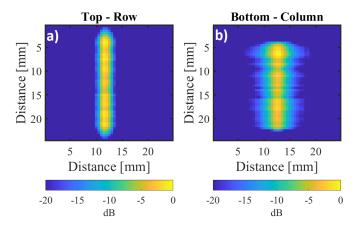

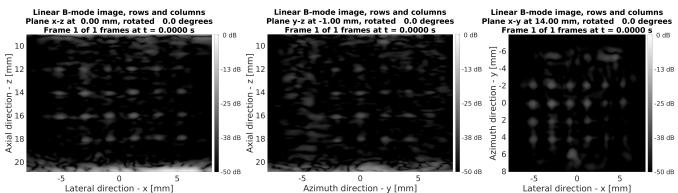

#### 2.1 Determining CMUT design parameters